#### INTEGRATED CIRCUITS

# Semiconductors for Wireless Communications

http://www.semiconductors.philips.com

Applications Handbook IC17b 1998

Let's make things better.

**PHILIPS**

#### **QUALITY ASSURED**

Our quality system focuses on the continuing high quality of our components and the best possible service for our customers. We have a three-sided quality strategy: we apply a system of total quality control and assurance; we operate customer-oriented dynamic improvement programmes; and we promote a partnering relationship with our customers and suppliers.

#### PRODUCT SAFETY

In striving for state-of-the-art perfection, we continuously improve components and processes with respect to environmental demands. Our components offer no hazard to the environment in normal use when operated or stored within the limits specified in the data sheet.

Some components unavoidably contain substances that, if exposed by accident or misuse, are potentially hazardous to health. Users of these components are informed of the danger by warning notices in the data sheets supporting the components. Where necessary the warning notices also indicate safety precautions to be taken and disposal instructions to be followed. Obviously users of these components, in general the set-making industry, assume responsibility towards the consumer with respect to safety matters and environmental demands.

All used or obsolete components should be disposed of according to the regulations applying at the disposal location. Depending on the location, electronic components are considered to be 'chemical', 'special' or sometimes 'industrial' waste. Disposal as domestic waste is usually not permitted.

#### **CONTENTS**

|                         | Page |

|-------------------------|------|

| PREFACE                 | 3    |

| INDEX                   | 5    |

| SELECTION GUIDE         | 9    |

| INTRODUCTION            | 57   |

| GENERAL                 | 77   |

| APPLICATION INFORMATION | 87   |

| DATA HANDBOOK SYSTEM    | 663  |

#### **DEFINITIONS**

| This data sheet contains target or goal specifications for product development.                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| This data sheet contains preliminary data; supplementary data may be published later.                                                                                          |

| This data sheet contains final product specifications.                                                                                                                         |

| The data in this specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook. |

|                                                                                                                                                                                |

#### Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

#### Application information

Where application information is given, it is advisory and does not form part of the specification.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

#### PURCHASE OF PHILIPS I2C COMPONENTS

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specification defined by Philips. This specification can be ordered using the code 9398 393 40011.

#### **PREFACE**

#### Semiconductors for Wireless Communications

Welcome to the latest edition of our Data Handbook "Semiconductors for Wireless Communications". Wireless communications is one of the fastest growing markets segments in the electronics business today. And no one has more to offer in this area than Philips Semiconductors. We supply semiconductor components for everything from cordless, cellular and paging products to exciting new applications, like wireless LAN, Personal Communications Systems (PCS), Global Positioning System (GPS), audio products, industrial control, security systems, and more.

What better place to start, therefore, with your search of wireless communication devices than with this Data Handbook. To make selections easier, we have split the book into two parts, parts a and b. In part a, you'll find IC selection charts, wireless system solutions and all our current wireless semiconductor data sheets. As a further aid, we can also supply all these data sheets on a separately available CD-ROM. To supplement this data, part b of the Data Handbook contains a selection of wireless application reports. These reports give detailed design examples, in-depth system information and practical advice on how to get the most from our wireless semiconductors.

For more information on how we can help with your wireless designs, or to speak to a local sales representative, in the U.S. call 1 800 447 1500, ext. 1253; in Europe fax +31 40 272 4825; in Asia/Pacific fax +852 319 7890, or in Japan fax +81 3 3740 5057. Or visit our worldwide web site at http://www.semiconductors.philips.com

#### **INDEX**

Index

|         |                                                                                  | PAGE |

|---------|----------------------------------------------------------------------------------|------|

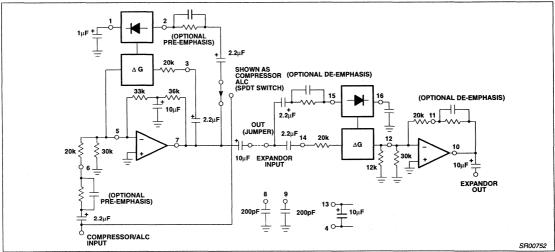

| AN174   | Applications for compandors NE570/571/SA571                                      | 88   |

| AN175   | Automatic level control using the NE572                                          | 98   |

| AN176   | Compandor cookbook                                                               | 99   |

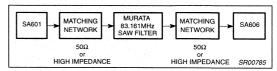

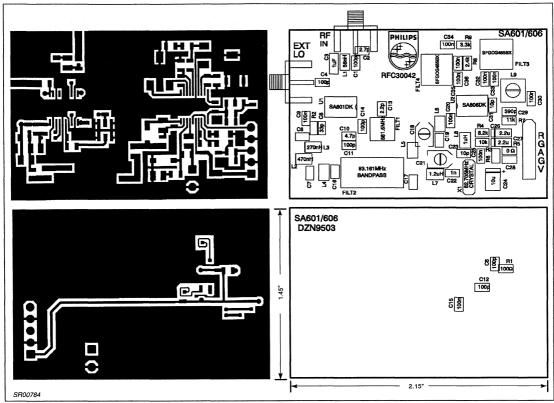

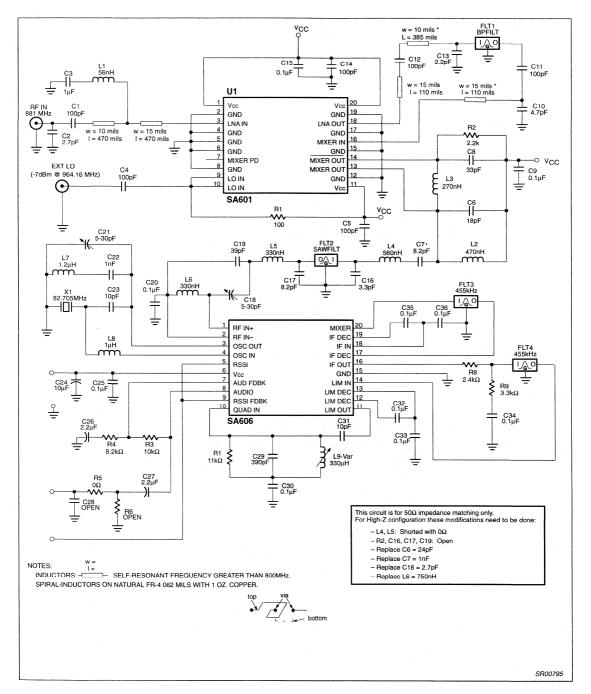

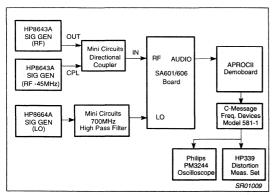

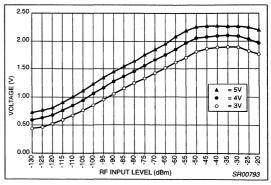

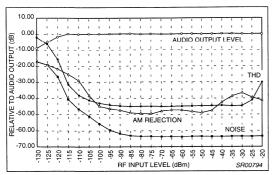

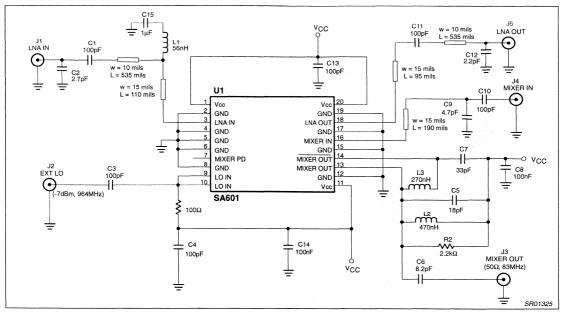

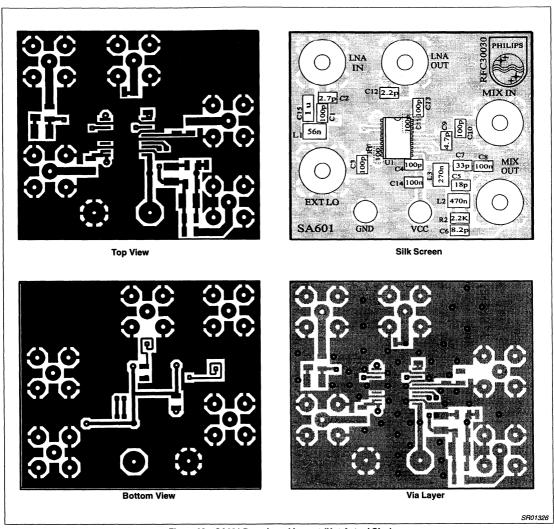

| AN1000  | Evaluation of the SA601, SA606 Demo board                                        | 105  |

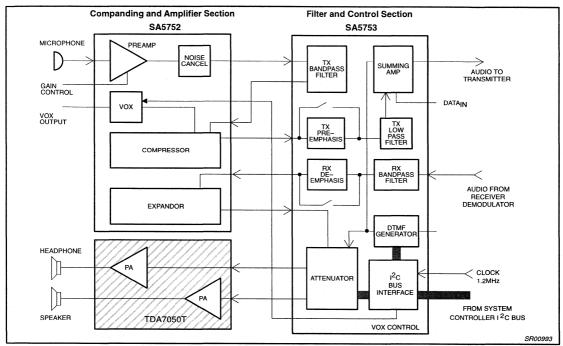

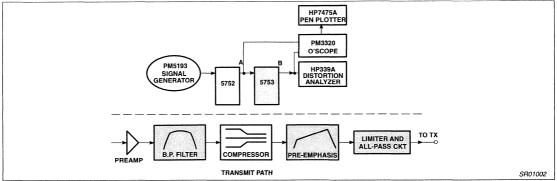

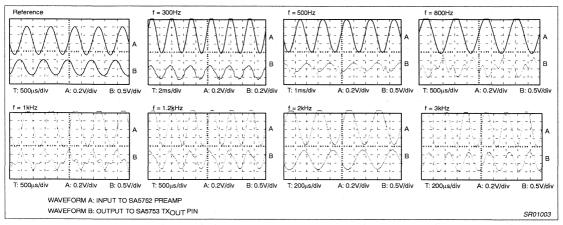

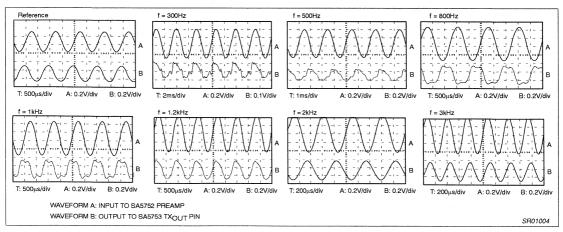

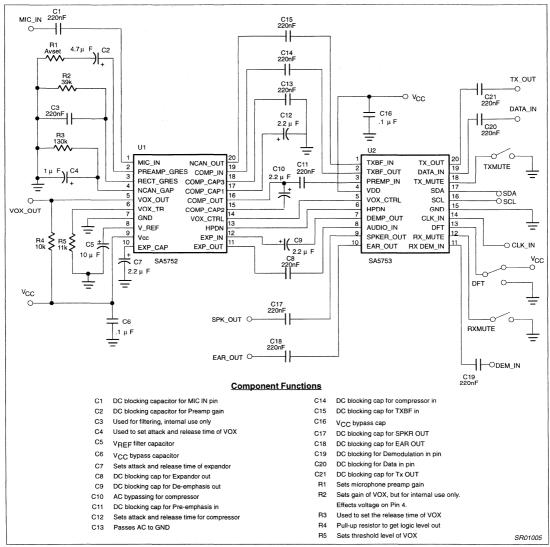

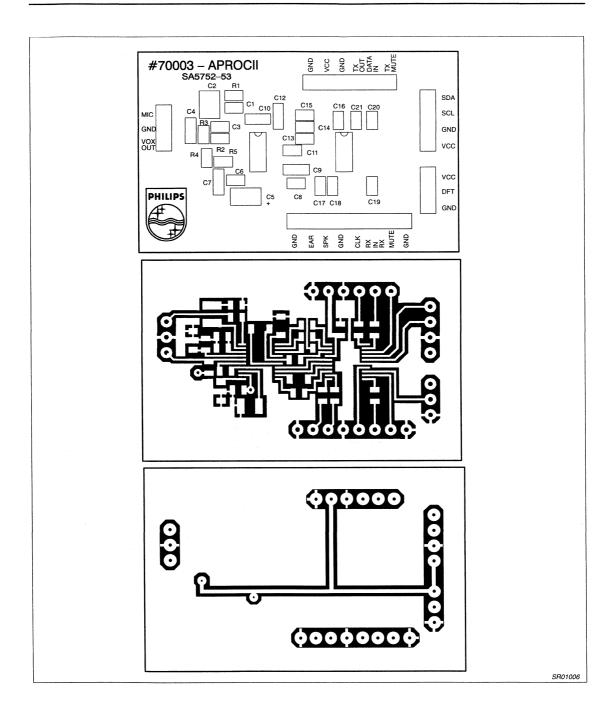

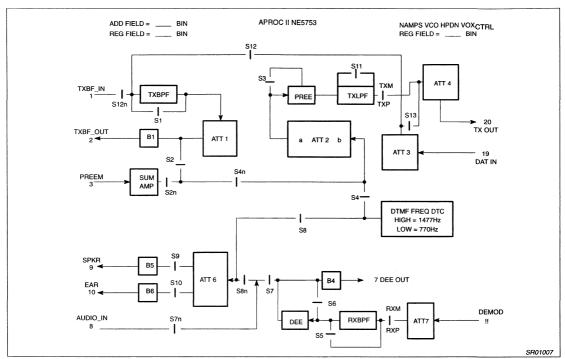

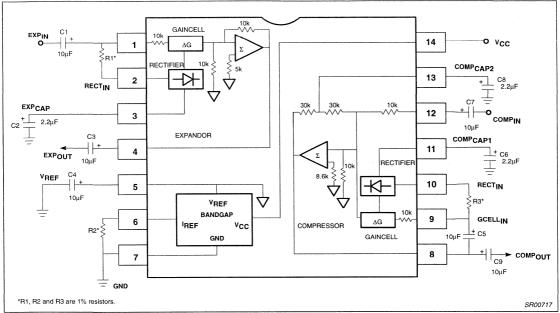

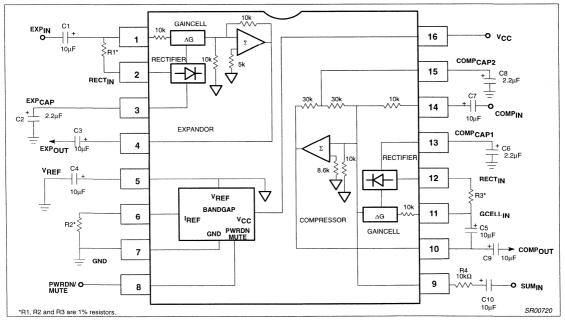

| AN1742  | Using the SA5752 and SA5753 for low-voltage designs                              | 122  |

| AN1762  | Companding with the NE577 and NE578                                              | 139  |

| AN1777  | Low-voltage frontend circuits: SA601, SA620                                      | 153  |

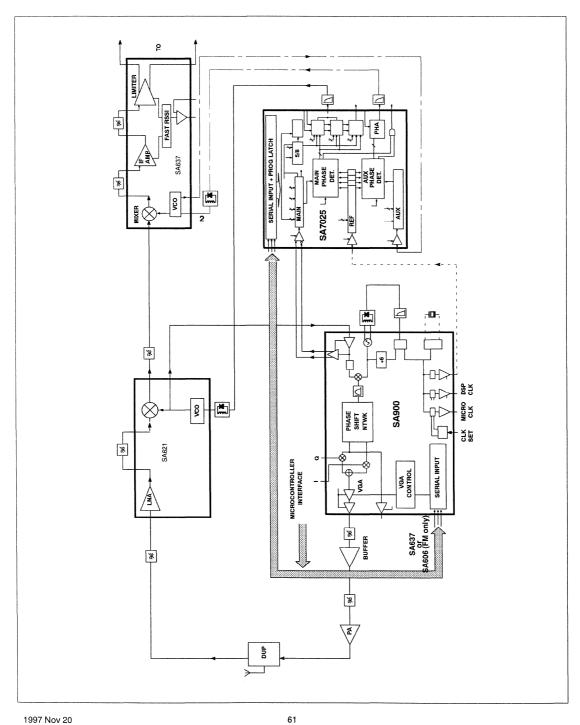

| AN1890  | Using the SA7025(revA) and the SA8025A for narrow band systems                   | 183  |

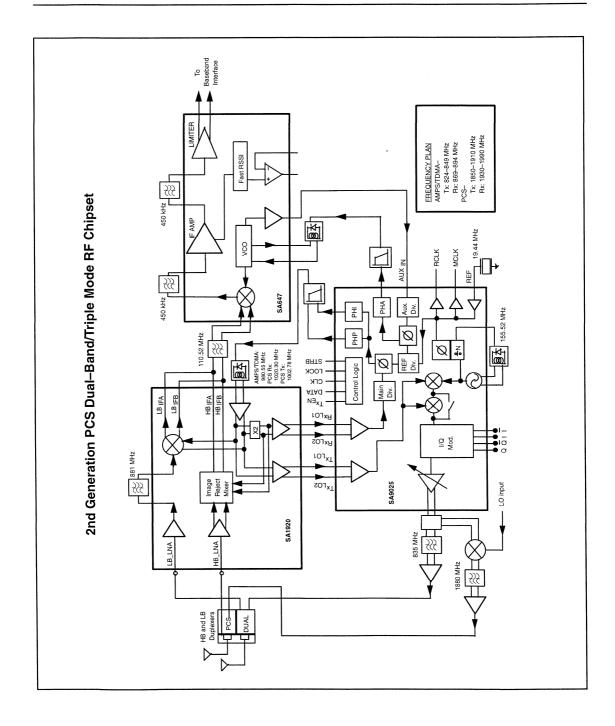

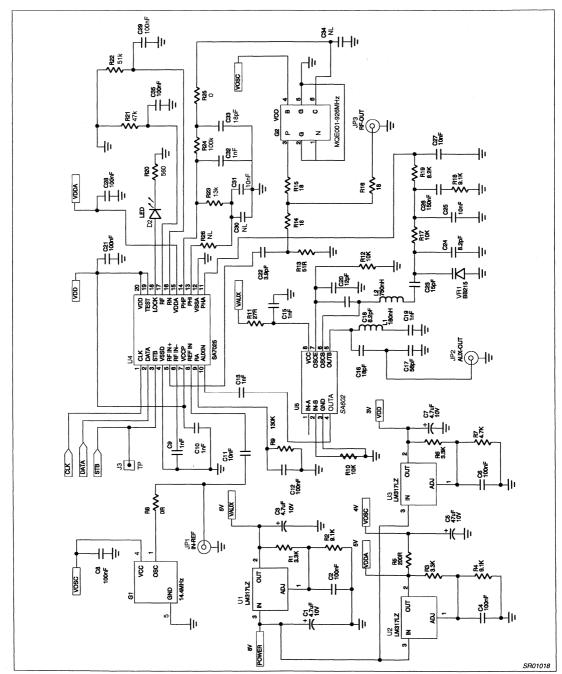

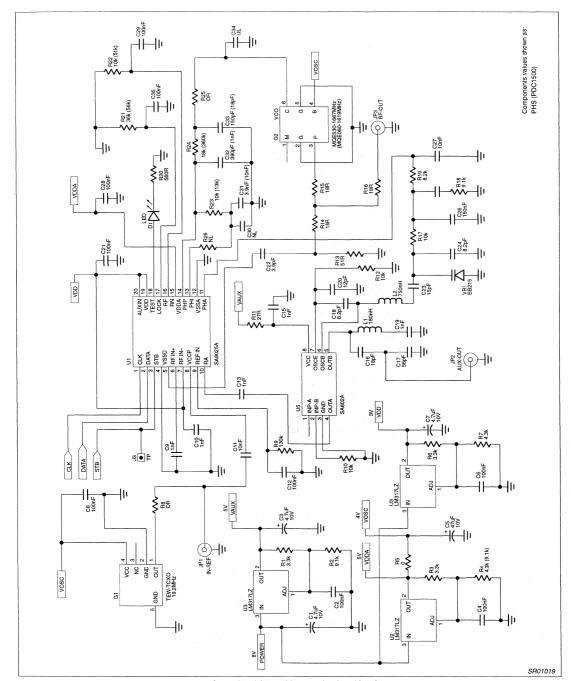

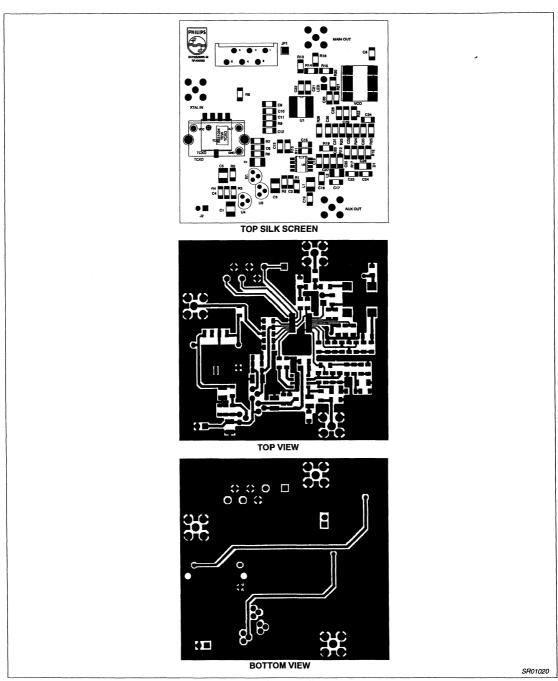

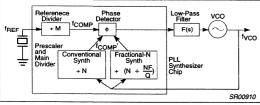

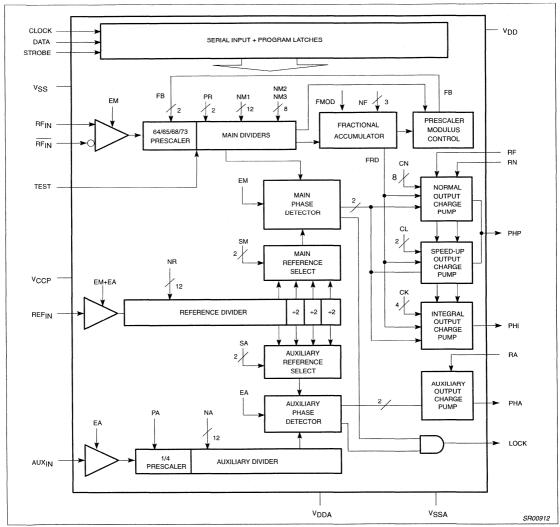

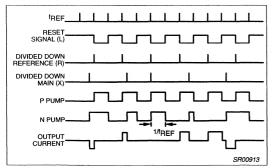

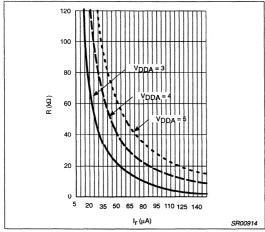

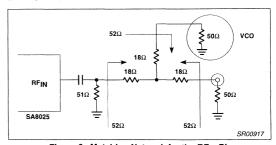

| AN1891  | SA8025 fractional-N synthesizer for 2GHz band applications                       | 195  |

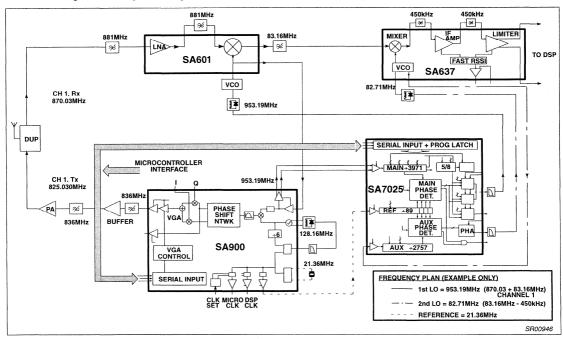

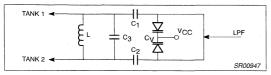

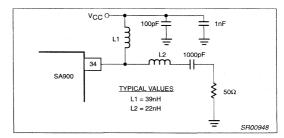

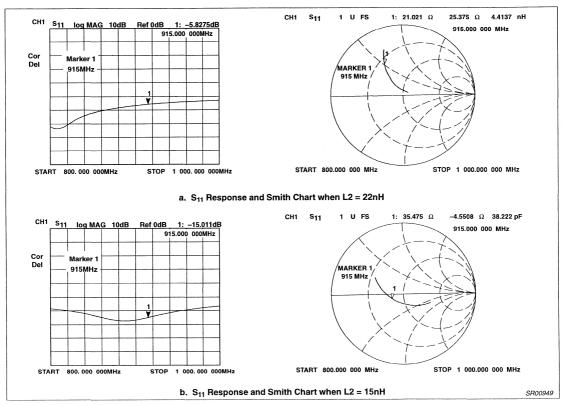

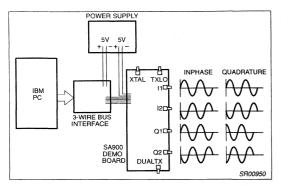

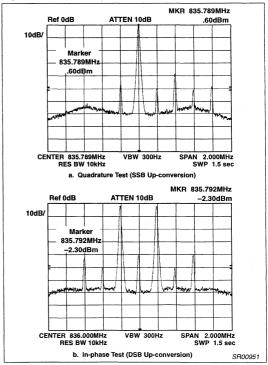

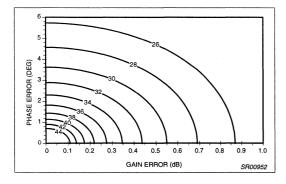

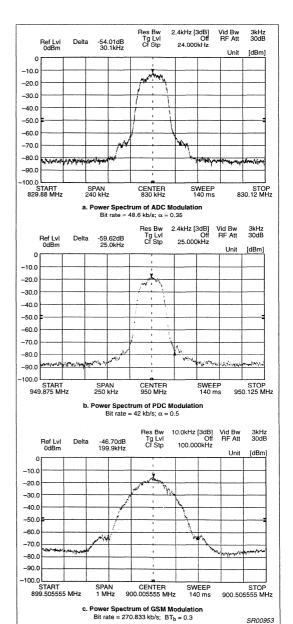

| AN1892  | SA900 I/Q transmit modulator for 1GHz applications                               | 209  |

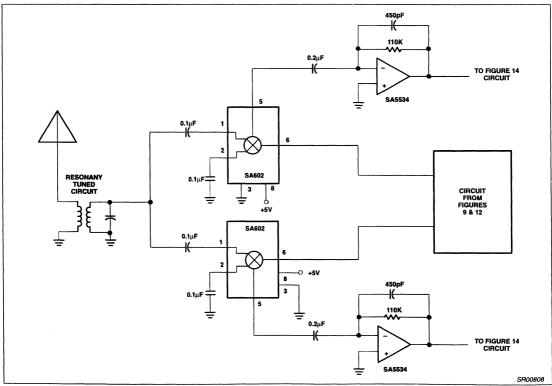

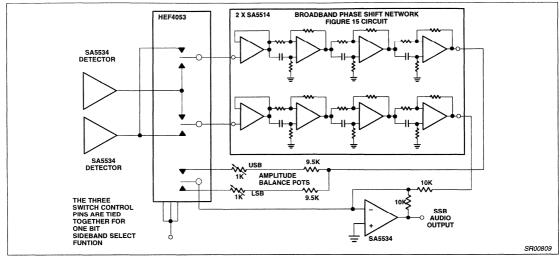

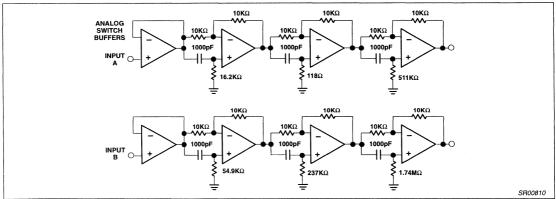

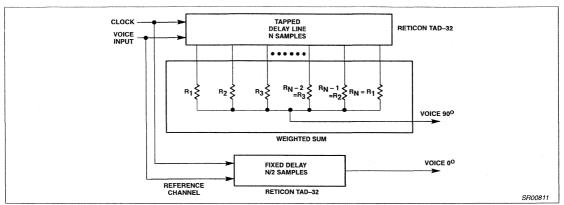

| AN1981  | New low-power single sideband circuits                                           | 222  |

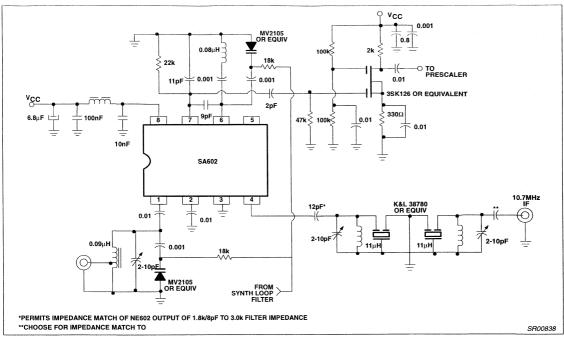

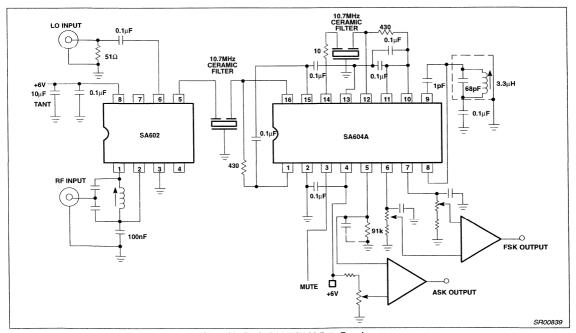

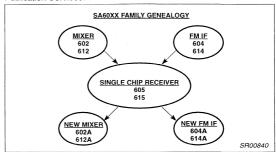

| AN1982  | Applying the oscillator of the NE602 in low-power mixer applications             | 231  |

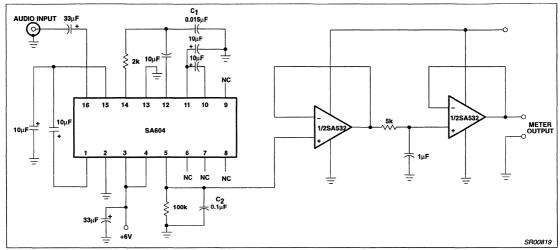

| AN1991  | Audio decibel level detector with meter driver                                   | 235  |

| AN1993  | High sensitivity applications of low-power RF/IF integrated circuits             | 237  |

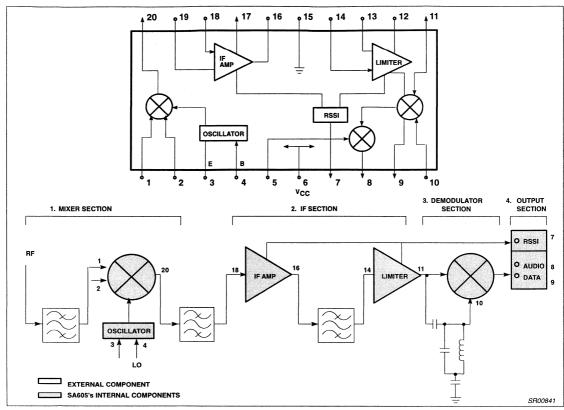

| AN1994  | Reviewing key areas when designing with the NE605                                | 249  |

| AN1995  | Evaluating the NE605 SO and SSOP demo-board                                      | 270  |

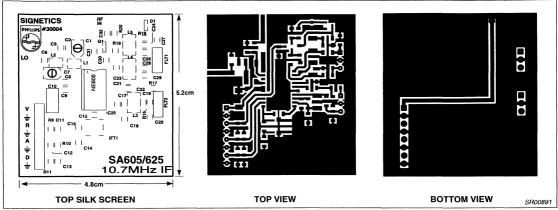

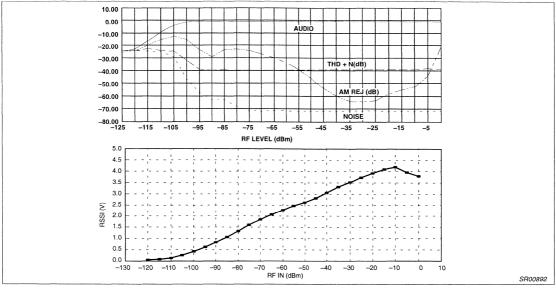

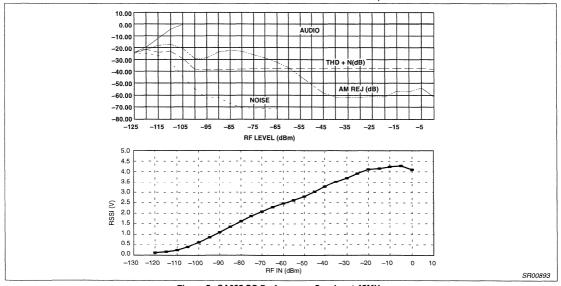

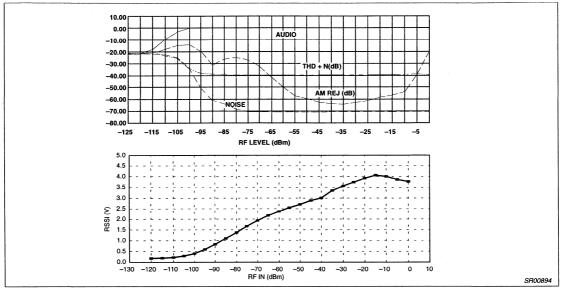

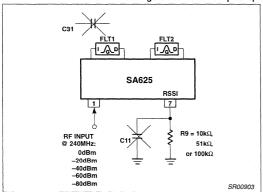

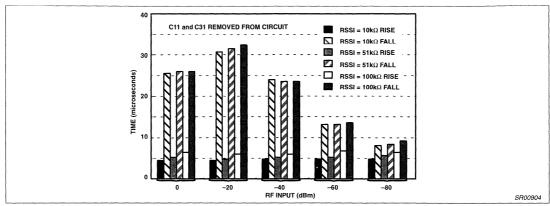

| AN1996  | Demodulating at 10.7MHz IF with the NE/SA605/625                                 | 280  |

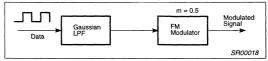

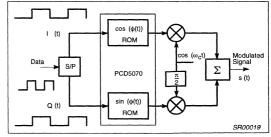

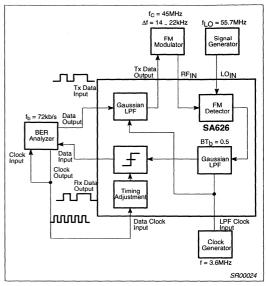

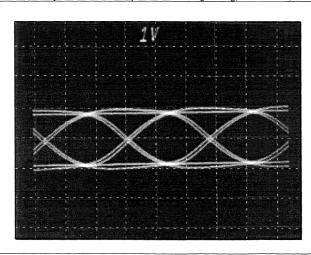

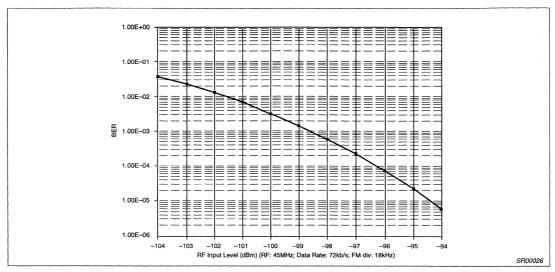

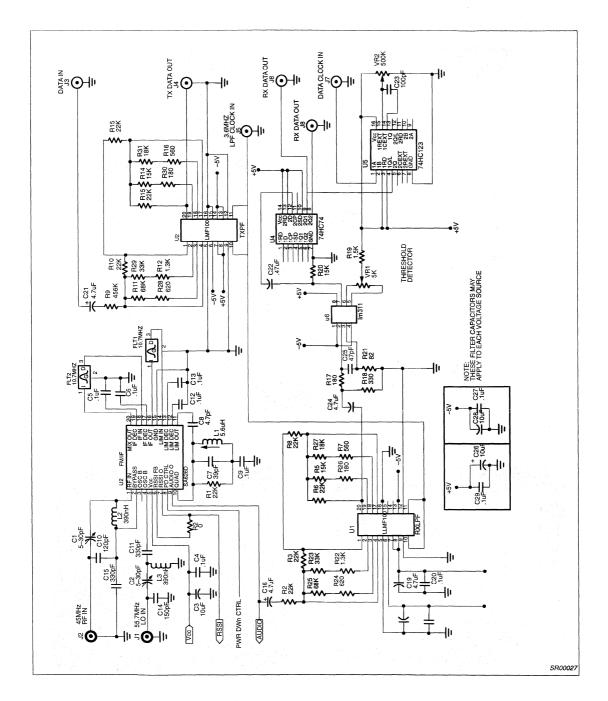

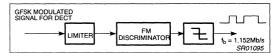

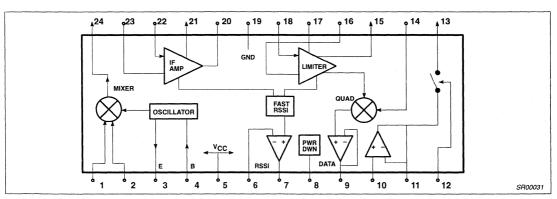

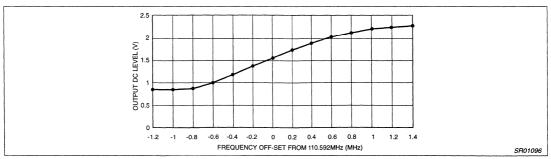

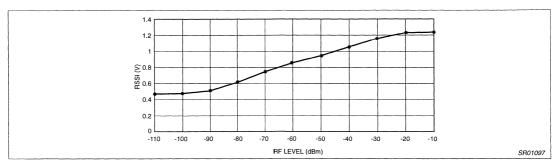

| AN1997  | Philips FM/IF systems for GMSK/GFSK receivers                                    | 293  |

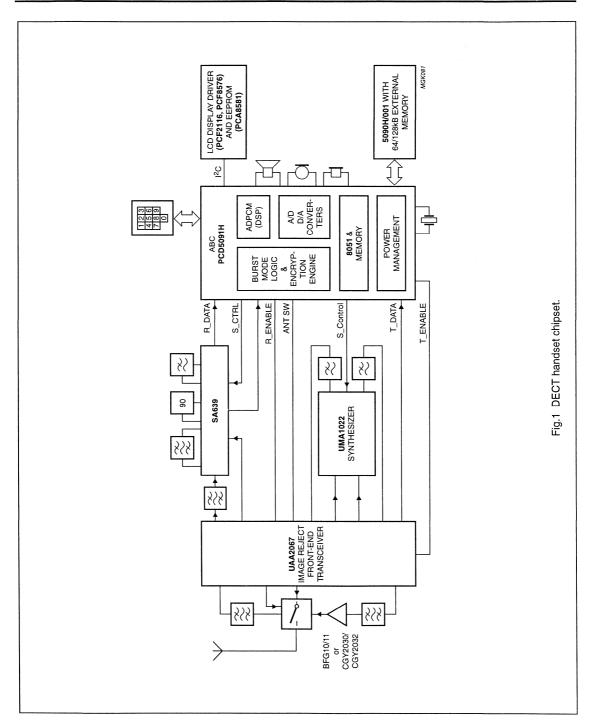

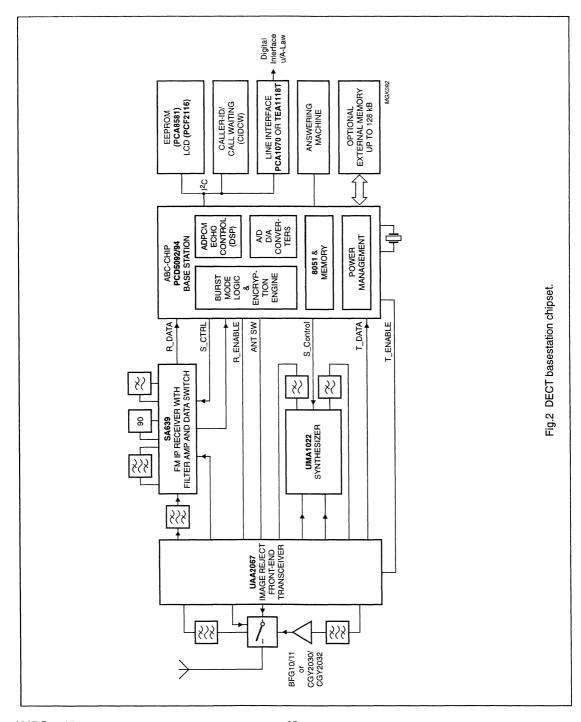

| AN1998  | An FM/IF system for DECT and other hi speed GFSK applications: SA639             | 302  |

| AN2000  | Techniques for optimizing UHF front-end integrated circuits                      | 311  |

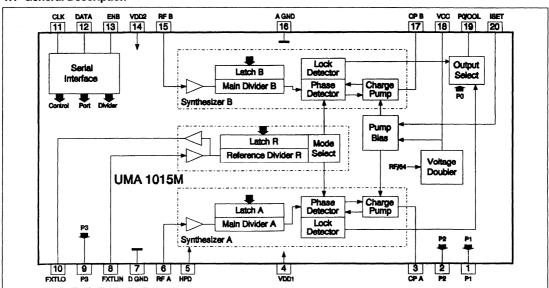

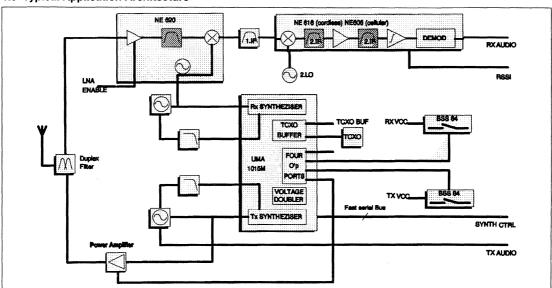

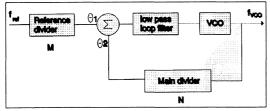

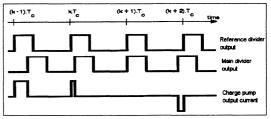

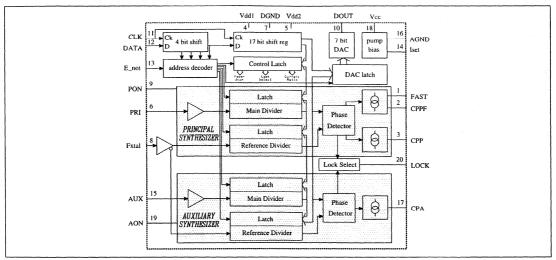

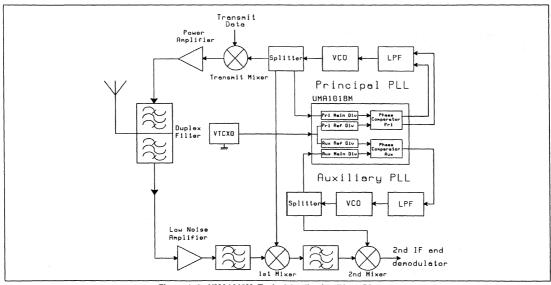

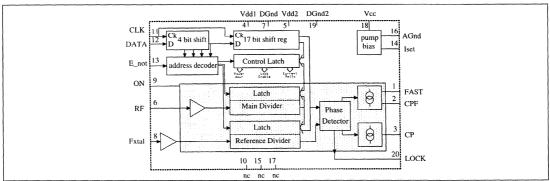

| AN93016 | UMA1015M low power dual 1GHz frequency synthesizer                               | 332  |

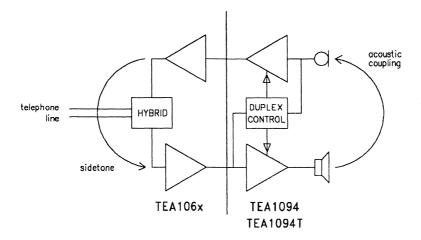

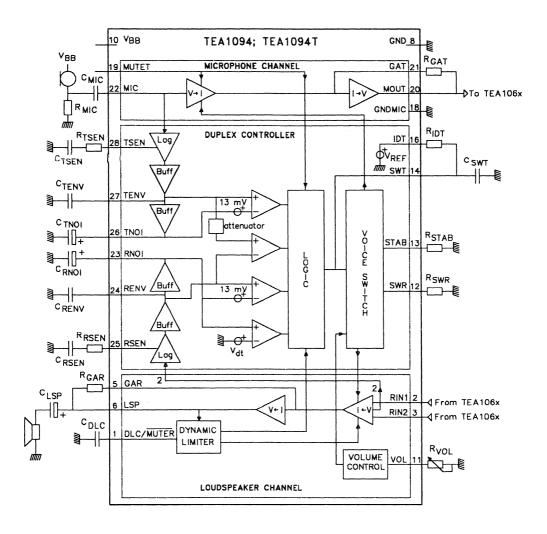

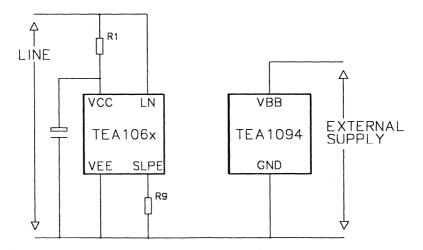

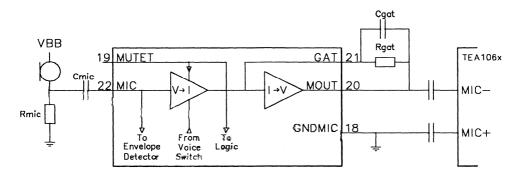

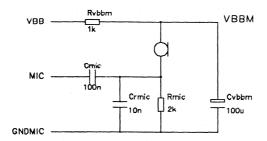

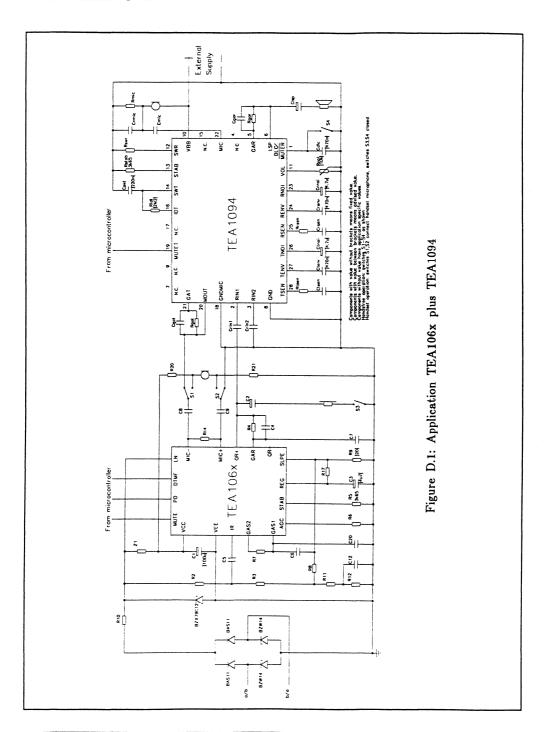

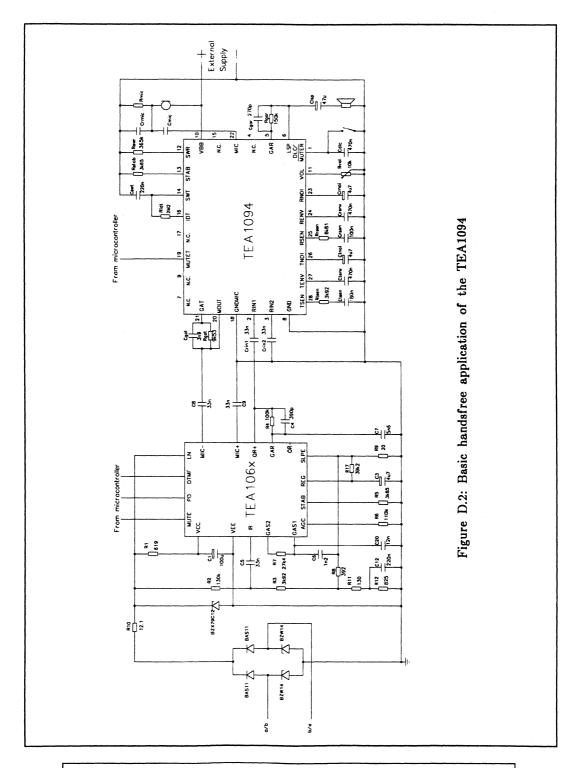

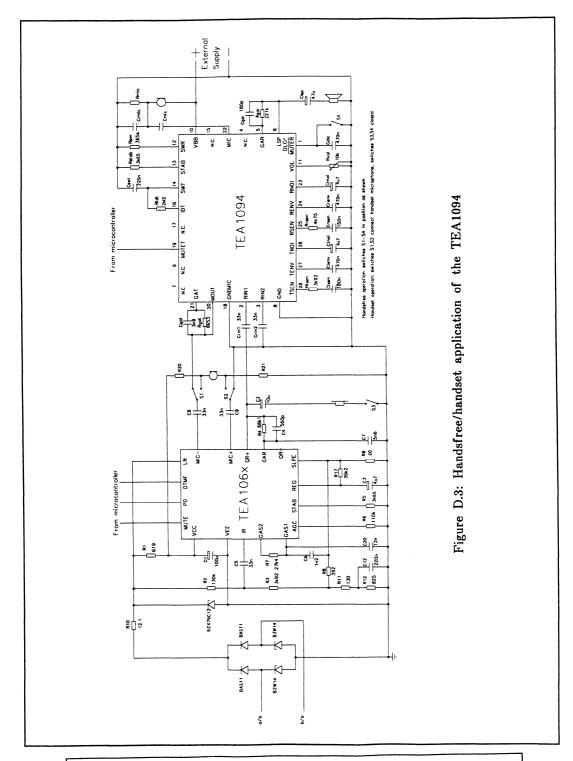

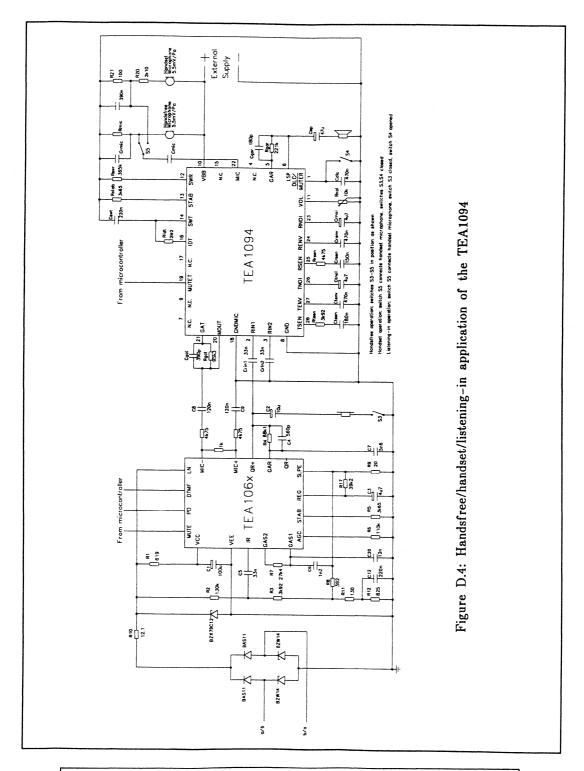

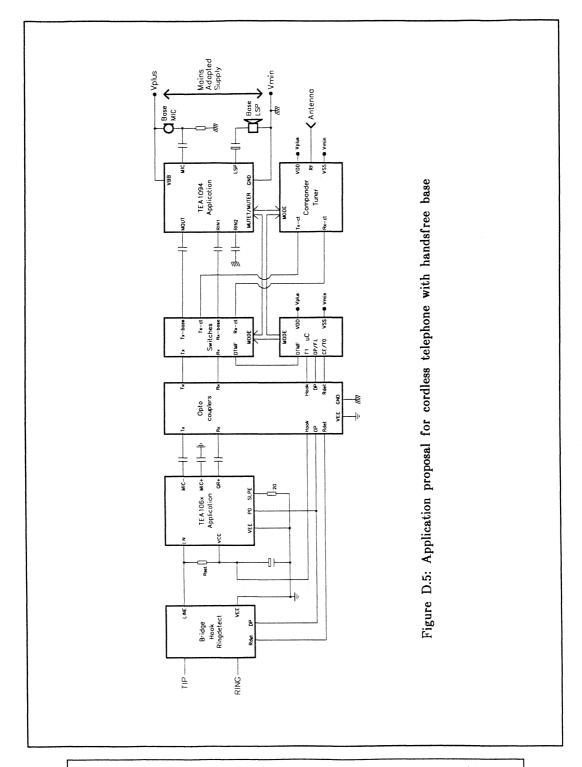

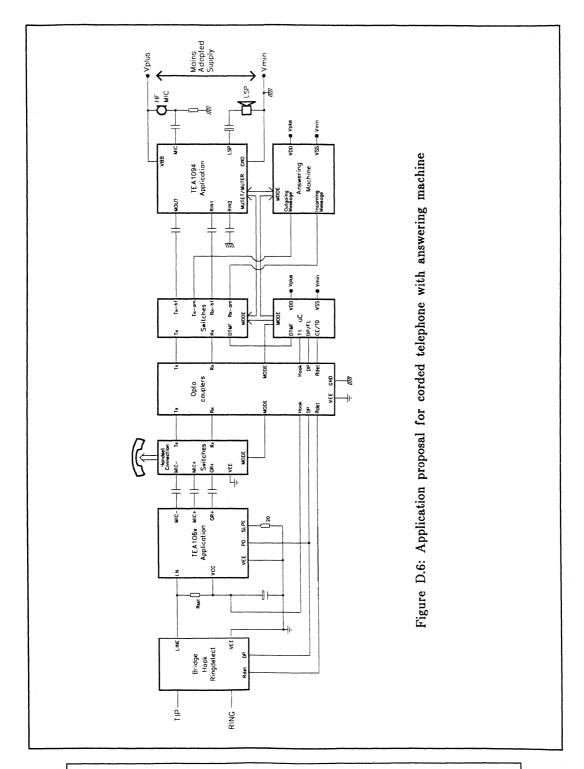

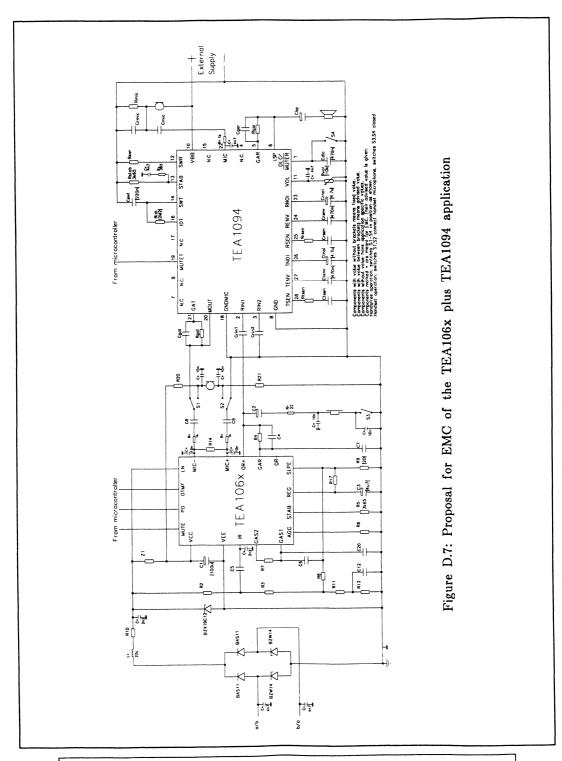

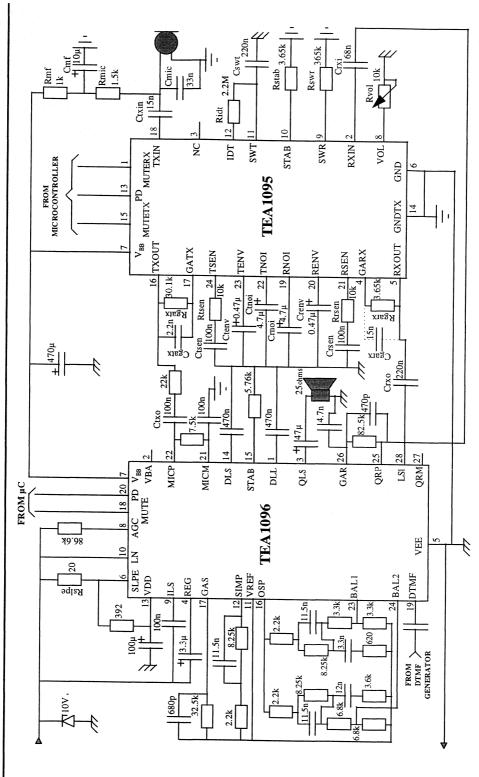

| AN94004 | Application of the TEA1094 handsfree circuit                                     | 336  |

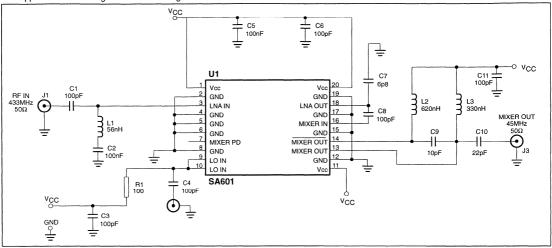

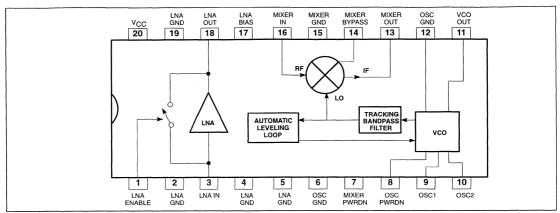

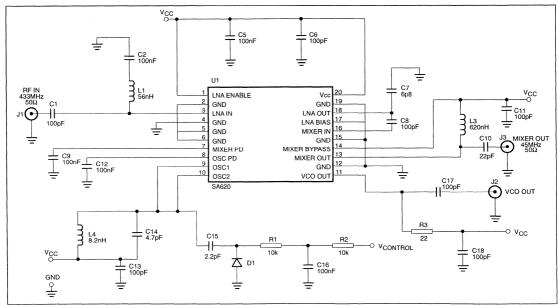

| AN95021 | 433MHz front end with the SA601 or SA620                                         | 399  |

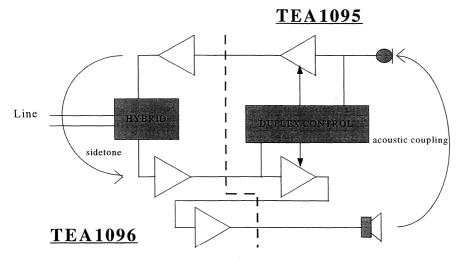

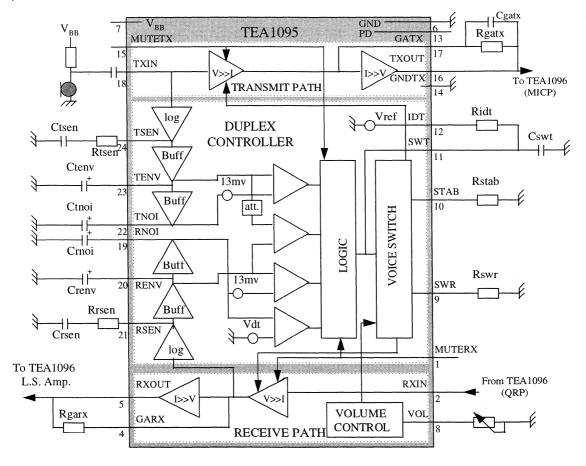

| AN95083 | Application of the TEA1095 voice-switched speaker phone IC                       | 404  |

| AN95102 | Low power single/dual frequency synthesizers: UMA1017M;1018M;1019M(AM);1020M(AM) | 444  |

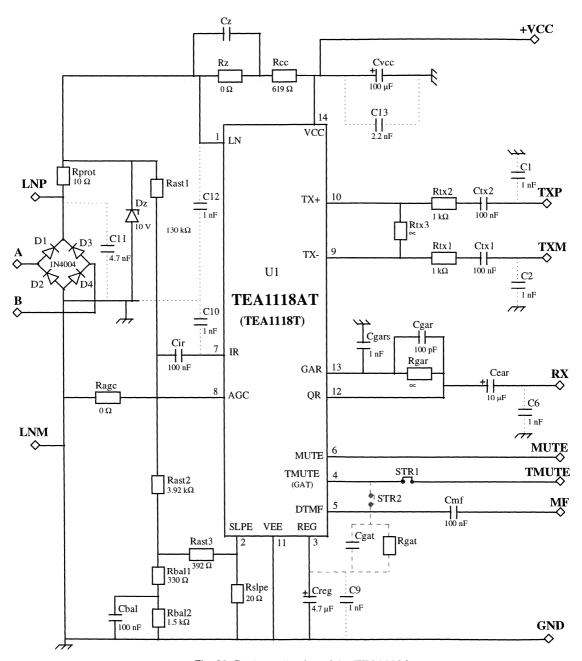

| AN96071 | Application of the TEA1118/A versatile cordless transmission circuit             | 471  |

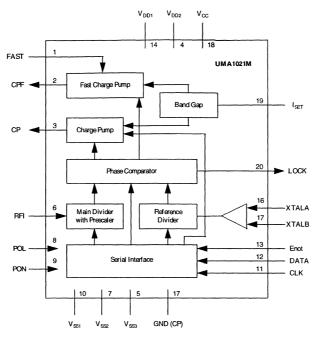

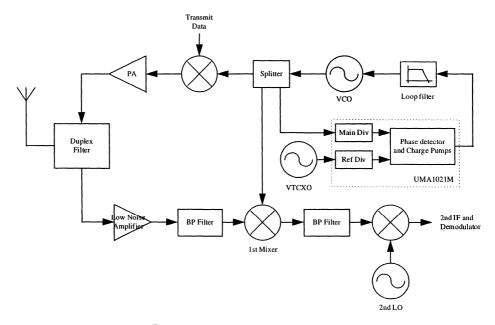

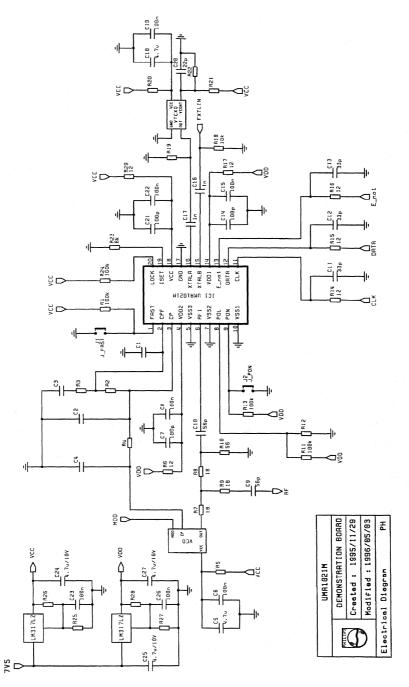

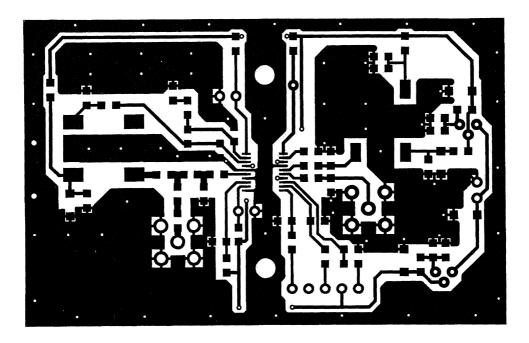

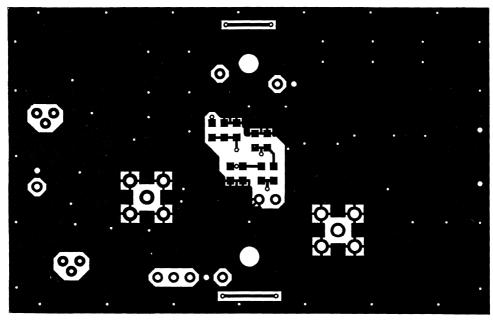

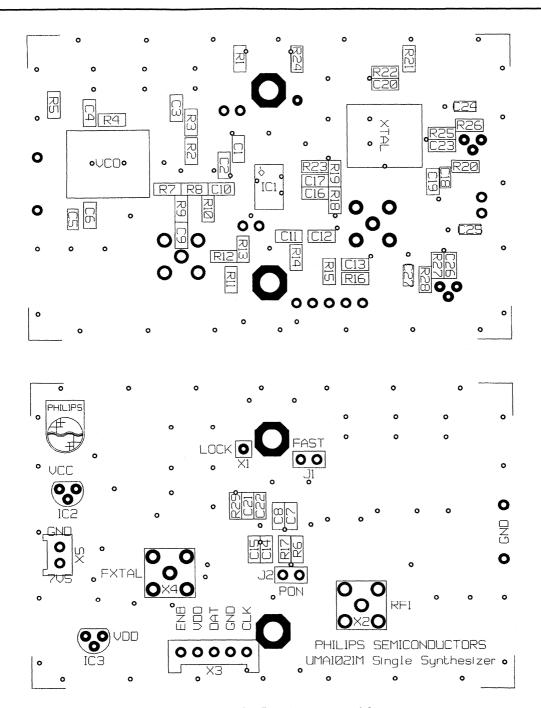

| AN96083 | Application of the low voltage single frequency synthesizer UMA1021M             | 507  |

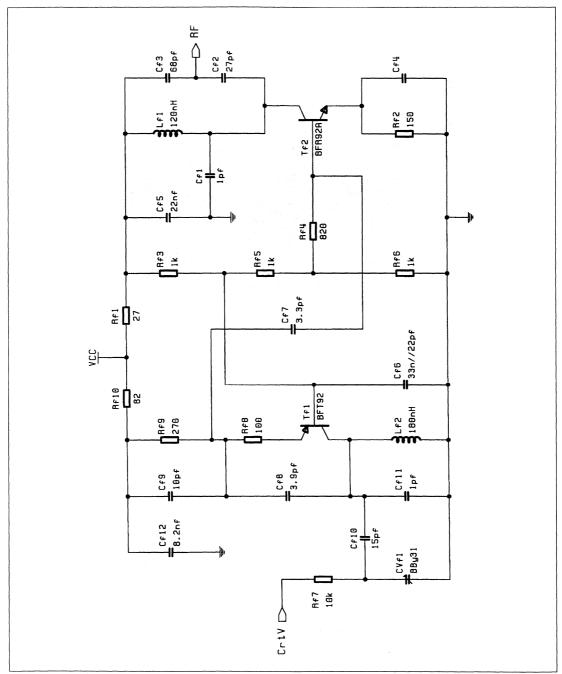

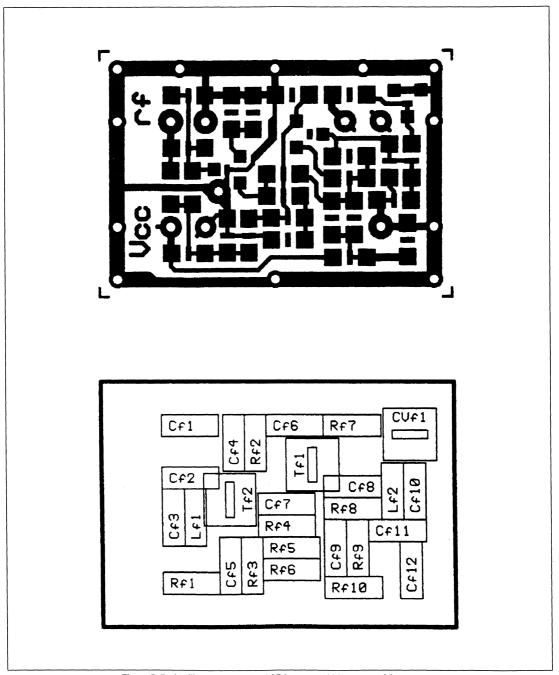

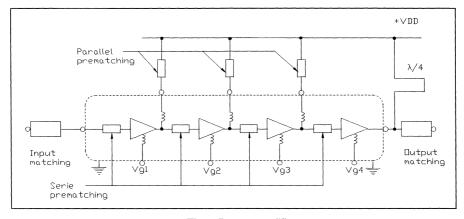

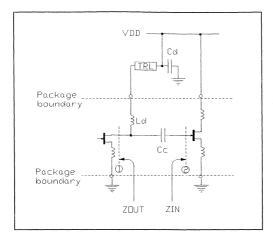

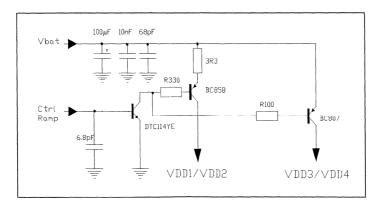

| AN96084 | Application note for CGY2030M power amplifier                                    | 568  |

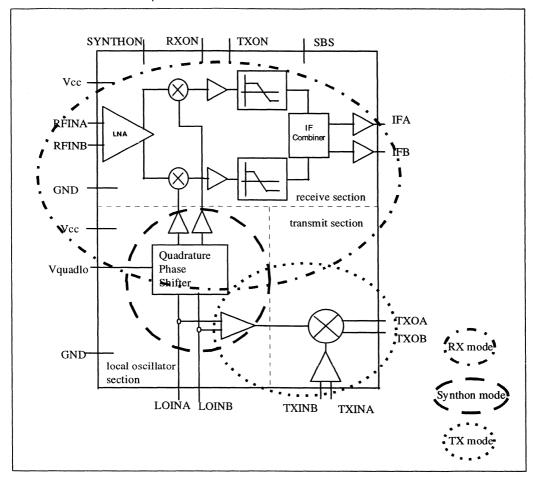

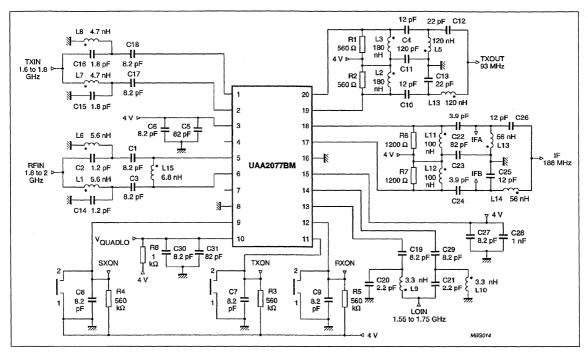

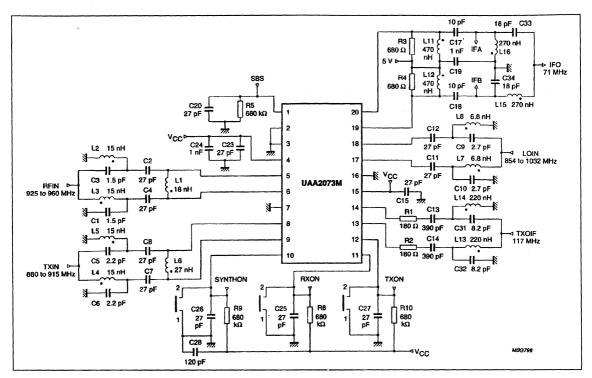

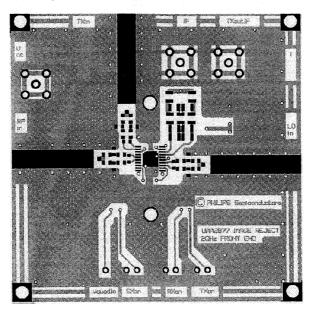

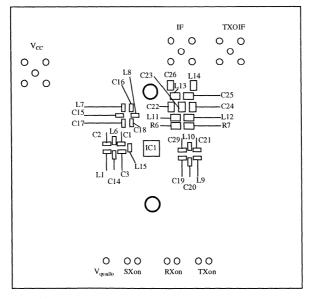

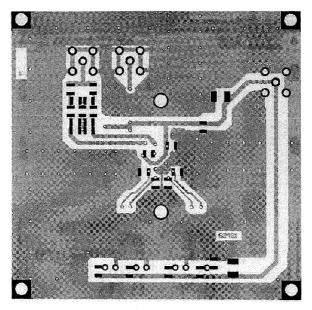

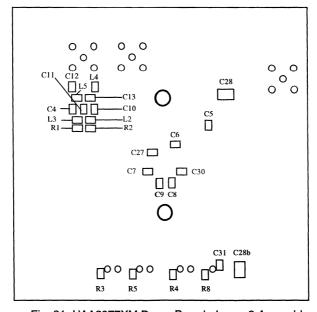

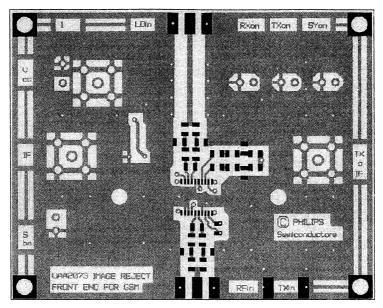

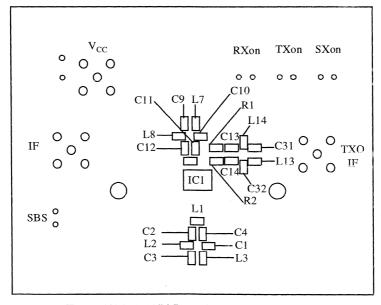

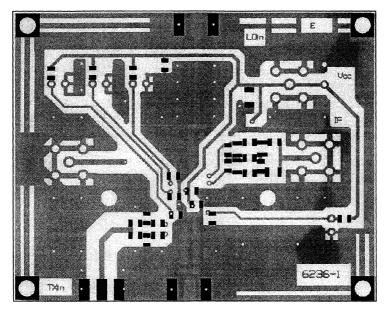

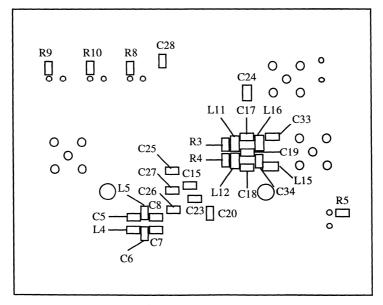

| AN96106 | Application of the UAA2072/73/77AM/77BM Image rejecting front-ends               | 584  |

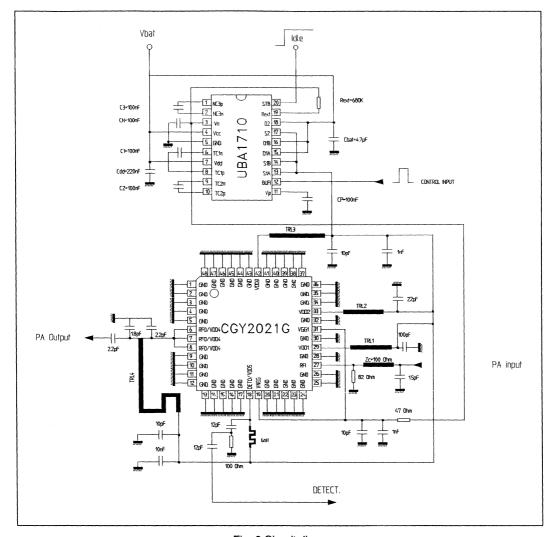

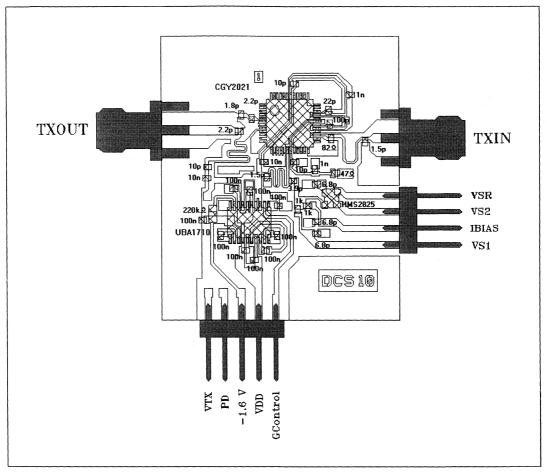

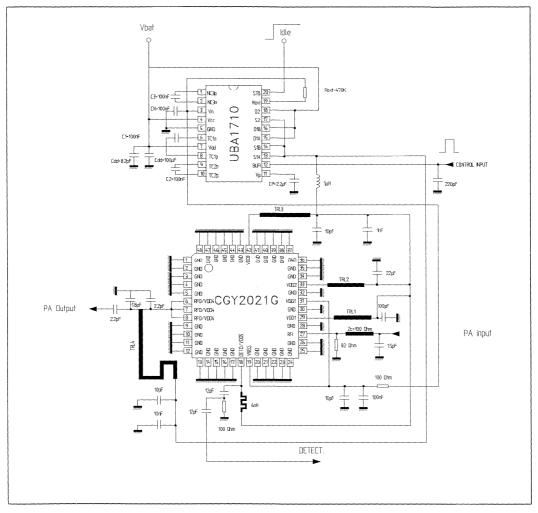

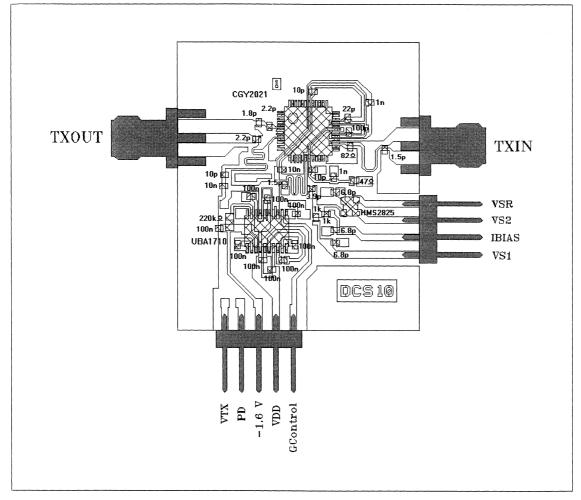

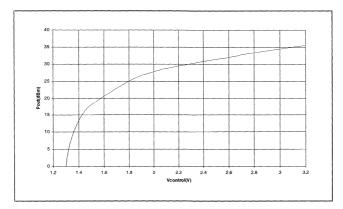

| AN97034 | Application of the CGY2021G power amplifier                                      | 622  |

| AN97077 | Application of the UBA1710M modulator for GSM/DCS/PCS amplifiers                 | 644  |

#### **SELECTION GUIDE**

|                                         | Page |

|-----------------------------------------|------|

| Functional index                        | S    |

| Replacement list                        | 12   |

| Ordering information                    | 15   |

| System standard -Product selector guide | 16   |

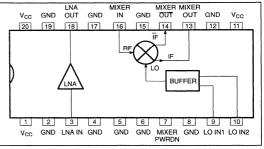

| Front-end, Integrated                   | 18   |

| Front-end, Discrete                     | 22   |

| IF systems                              | 23   |

| Frequency synthesizers                  | 26   |

| Transmitters ICs                        | 29   |

| MMICs Amplifiers                        | 30   |

| Module Amplifiers                       | 31   |

| Discrete Amplifiers                     | 32   |

| Baseband processors                     | 34   |

| Compandors                              | 35   |

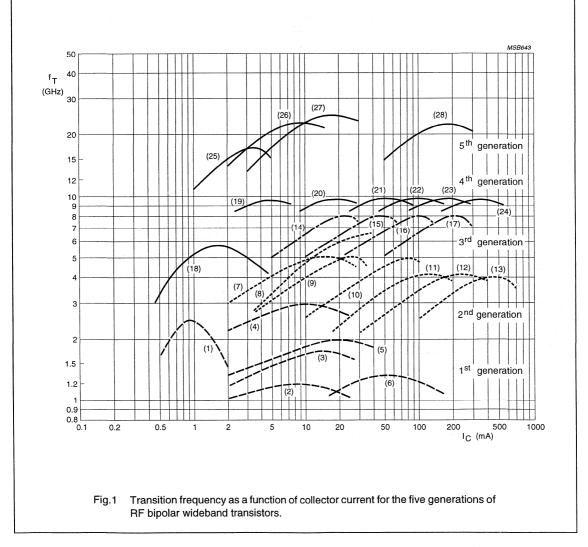

| RF wideband transistors                 | 37   |

| MOSFETs                                 | 53   |

| Internet WWW homepage                   | 54   |

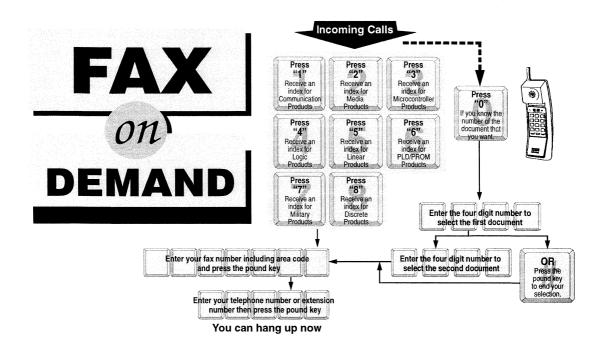

| Fax-on-Demand                           | 55   |

#### **Functional index**

|                  |                                                                                  | PAGE |

|------------------|----------------------------------------------------------------------------------|------|

| Front-ends       |                                                                                  |      |

| AN1000           | Evaluation of the SA601, SA606 Demo board                                        | 105  |

| AN1777           | Low voltage front-end circuits: SA601, SA620                                     | 153  |

| AN1981           | New low-power single sideband circuits                                           | 222  |

| AN1982           | Applying the oscillator of the NE602 in low-power mixer applications             | 231  |

| AN2000           | Techniques for optimizing UHF front-end integrated circuits                      | 311  |

| AN95021          | 433MHz front-end with the SA601 or SA620                                         | 399  |

| AN96106          | Application of the UAA2072/73/77AM/77BM Image rejecting front-ends               | 584  |

| IF Systems       |                                                                                  |      |

| AN1991           | Audio decibel level detector with meter driver                                   | 235  |

| AN1993           | High sensitivity applications of low-power RF/IF integrated circuits             | 237  |

| AN1994           | Reviewing key areas when designing with the NE605                                | 249  |

| AN1995           | Evaluating the NE605 SO and SSOP demo board                                      | 270  |

| AN1996           | Demodulating at 10.7MHz IF with the NE/SA605/625                                 | 280  |

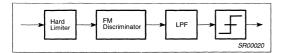

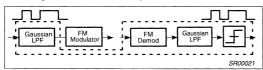

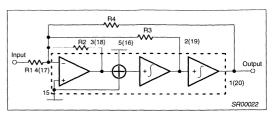

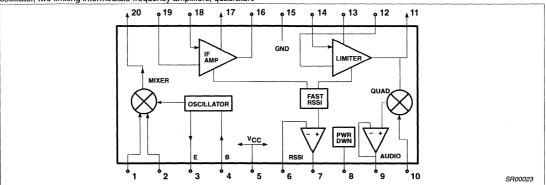

| AN1997           | Philips FM/IF systems for GMSK/GFSK receivers                                    | 293  |

| AN1998           | An FM/IF system for DECT and other hi-speed GFSK applications: SA639             | 302  |

| Frequency Synthe | esizers and Prescalers                                                           |      |

| AN1890           | Using the SA7025(revA) and the SA8025A for narrow band systems                   | 183  |

| AN1891           | SA8025 fractional-N synthesizer for 2GHz band applications                       | 195  |

| AN93016          | UMA1015M low-power dual 1GHz frequency synthesizer                               | 332  |

| AN95102          | Low-power single/dual frequency synthesizers: UMA1017M;1018M;1019M(AM);1020M(AM) | 444  |

| AN96083          | Application of the low-voltage sigle frequency synthesizer UMA1021M              | 507  |

| Power Amplifiers | , Transmitters, and Switches                                                     |      |

| AN1892           | SA900 I/Q transmit modulator for 1GHz applications                               | 209  |

| AN96084          | Application note for CGY2030M power amplifier                                    | 568  |

| AN97034          | Application of the CGY2021G power amplifier                                      | 622  |

| AN97077          | Application of the UBA1710M                                                      | 644  |

1997 Dec 15

#### Functional index

|                    |                                                                      | PAGE |

|--------------------|----------------------------------------------------------------------|------|

| Baseband Processir | ng: Audio and Data                                                   |      |

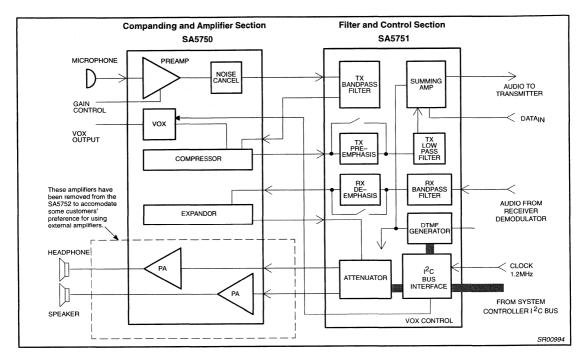

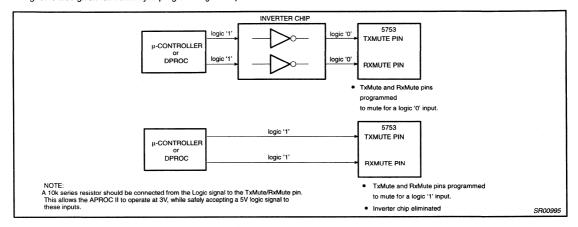

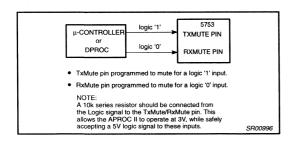

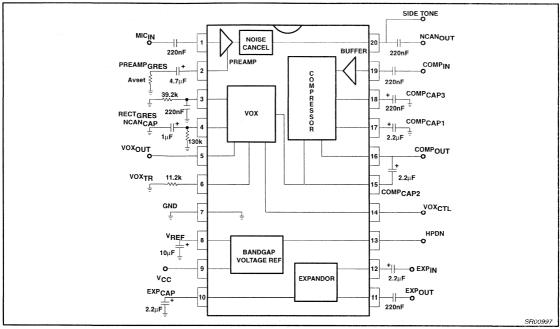

| AN1742             | Using the SA5752 and SA5753 for low-voltage designs                  | 122  |

| AN94004            | Application of the TEA1094 hands free circuit                        | 336  |

| AN95083            | Application of the TEA1095 voice-switched speaker phone IC           | 404  |

| AN96071            | Application of the TEA1118/A versatile cordless transmission circuit | 471  |

| Compandors         |                                                                      |      |

| AN174              | Applications for compandors NE570/571/SA571                          | 88   |

| AN175              | Automatic level control using the NE572                              | 98   |

| AN176              | Compandor cookbook                                                   | 99   |

| AN1762             | Companding with the NE577 and NE578                                  | 139  |

1997 Dec 15

#### Replacement list

#### **REPLACED/WITHDRAWN TYPES**

The following type numbers were included in the previous issue of this data handbook, but are not in the current edition.

| YPE NUMBER REASON FOR DELETION |                               |  |

|--------------------------------|-------------------------------|--|

| CGY2010G                       | Nearest replacement: CGY2013G |  |

| CGY2011G                       | Nearest replacement: CGY2013G |  |

| CGY2023G                       | Nearest replacement: CGY2021G |  |

| NE570                          | Replaced by SA570             |  |

| NE571                          | Replaced by SA571             |  |

| NE572                          | Replaced by SA572             |  |

| NE575                          | Replaced by SA575             |  |

| NE576                          | Replaced by SA576             |  |

| NE577                          | Replaced by SA577             |  |

| NE578                          | Replaced by SA578             |  |

| NE600                          | Replaced by SA600             |  |

| NE602A                         | Replaced by SA602A            |  |

| NE604A                         | Replaced by SA604A            |  |

| NE605                          | Replaced by SA605             |  |

| NE612A                         | Replaced by SA612A            |  |

| NE614A                         | Replaced by SA614A            |  |

| NE615                          | Discontinued                  |  |

| NE624                          | Replaced by SA624             |  |

| NE625                          | Replaced by SA625             |  |

| NE627                          | Replaced by SA627             |  |

| NE630                          | Replaced by SA630             |  |

| NE5200                         | Replaced by SA5200            |  |

| NE5204A                        | Replaced by SA5204A           |  |

| NE5205A                        | Replaced by SA5205A           |  |

| NE5209                         | Replaced by SA5209            |  |

| NE5219                         | Replaced by SA5219            |  |

| NE/SA5750                      | Discontinued                  |  |

| NE/SA5751                      | Discontinued                  |  |

| PCA5097                        | Discontinued                  |  |

| PCD5032                        | Is not widely promoted        |  |

| PCD5090                        | Discontinued                  |  |

| PCD5097                        | Is not widely promoted        |  |

| PCF5075                        | Replaced by PCD5077           |  |

| TDA8780M                       | Discontinued                  |  |

| UAA2072M                       | Replaced by UAA2043M          |  |

1997 Dec 12 12

#### Replacement list

| TYPE NUMBER | REASON FOR DELETION                                 |

|-------------|-----------------------------------------------------|

| UMA1005T    | Not widely promoted                                 |

| UMA1014     | Not widely promoted. Nearest replacement: UMA1015AM |

| UMA1017M    | Not widely promoted. Nearest replacement: UMA1020M  |

| UMA1019AM   | Discontinued. Nearest replacement: UMA1021M         |

| UMA1019M    | Discontinued. Nearest replacement: UMA1021M         |

| UMA1020AM   | Discontinued. Nearest replacement: UMA1021M         |

#### **Ordering Information**

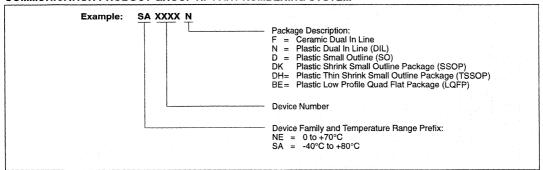

#### COMMUNICATION PRODUCT GROUP RF PART NUMBERING SYSTEM

#### PHILIPS PRODUCTS PART NUMBERING SYSTEM PREFIXES HE, PC, PN, SA, TD, TE, TS, UM

#### System Standard—Product Selector Guide

PAGERS Wireless Data CDPD 802.11 PHS DECT SS • 5 TARGET SYSTEMS CTO PDC • • PCS • DCS1800 GSM IS-95 CDMA IS-54/-136 TDMA (N)AMPS (E) TACS • Satellite/Cellular dual-band RF front-end 2.5GHz low voltage fractional—N dual frequency synthesizer \_ow-vottage, Fractional-N-1.04 GHz PCS/Cellular dual-band RF front-end Low-voltage, very low noise-2.2 GHz Low-voltage, Fractional-N-1.8 GHz Low voltage, very low noise-2.2 GHz 1.3GHz low voltage fractional-N dual frequency synthesizer 2.45GHz low voltage RF transceiver 1GHz low volt LNA, mixer and VCO Low voltage GSM RF transceiver Low-voltage, low noise-2.2 GHz 1.3GHz low voltage fractional-N synthesizer Low-voltage, single loop-2 GHz 2.5GHz low voltage fractional-N synthesizer Image reject front-end for DECT 1 GHz low volt LNA and mixer Image reject 1.8GHz for DECT 2GHz image reject front-end 2GHz image reject front-end Image reject GSM front-end Low-voltage, dual-1GHz Advanced pager receiver Advanced pager receiver Gain block-1 GHZ Description UAA2073(A)M UAA2077AM UAA2077CM UAA2077BM UMA1015AM UMA1018M UMA1020M UMA1021M UAA2067G UAA2080T Synthesizers/Prescalers UMA1022 UAA2082 SA8025A SA2420 SA1920 SA7016 SA5200 SA1620 SA1921 SA7025 SA8016 SA7026 SA8026 SA611 SA621 RF Amplifiers RF Front End

System Standard—Product Selector Guide

FSystem Standard—Product Selector Guide

| 1                                    |

|--------------------------------------|

|                                      |

| (N)AMPS IS-54/-136<br>/(E) TACS TDMA |

|                                      |

| ×                                    |

| •                                    |

|                                      |

|                                      |

|                                      |

|                                      |

|                                      |

|                                      |

| •                                    |

|                                      |

|                                      |

| •                                    |

|                                      |

|                                      |

|                                      |

|                                      |

|                                      |

|                                      |

<sup>&</sup>quot;e" = Recommended part-type/system solution

Alternate solution

#### Selection guide

#### FRONT-END, INTEGRATED CIRCUITSE

|                   | DESCRIPTION <sup>(3)</sup>                      | V <sub>CC</sub><br>(V) | I <sub>CC</sub><br>(mA)                  | PINS | Pkg <sup>(2)</sup> | INPUT<br>FREQUENCY                       |

|-------------------|-------------------------------------------------|------------------------|------------------------------------------|------|--------------------|------------------------------------------|

| lmage Reject F    | ront-End Systems                                |                        |                                          |      |                    |                                          |

| SA1920            | Dual-band<br>800/1900 MHz<br>LNA + IRM + IFamp. | 3.6 – 3.9              | HB Rx : 41.1<br>HB Tx : 21.3<br>@ 3.75 V | 48   | BE                 | 869 – 960 MHz<br>or<br>1.93-1.99 GHz     |

| SA1921            | Dual-band<br>900/1550 MHz<br>LNA + IRM + IFamp. | 3.6 – 3.9              | HB Rx : 38.6<br>HB Tx : 18.8<br>@ 3.75 V | 48   | BE                 | 935 – 960 MHz<br>or<br>1.525 – 1.559 GHz |

| UAA2067G          | LNA + IRM + Mod. +<br>VCO                       | 3 – 5.5                | Rx : 24<br>Tx : 42<br>@ 3.6 V            | 32   | BE                 | 1.8 – 1.9 GHz                            |

| UAA2077 <b>AM</b> | LNA + IRM                                       | 3.15 – 5.3             | 27 @ 4 V                                 | 20   | DK                 | 1.8 – 1.9 GHz                            |

| UAA2077BM         | LNA + IRM +<br>Tx down-convert mixer            | 3.6 – 5.3              | Rx : 27<br>Tx : 14<br>@ 4 V              | 20   | DK                 | 1.8 – 2 GHz                              |

| UAA2077CM         | LNA + IRM +<br>Tx down-convert mixer            | 3.6 – 5.3              | Rx : 36<br>Tx : 14<br>@ 3.75 V           | 20   | DK                 | 1.8 – 2 GHz                              |

| lmage Reject F    | ront-End Systems                                |                        |                                          |      |                    |                                          |

| UAA2073M          | LNA + IRM +<br>Tx down-convert mixer            | 3.6 – 5.3              | Rx : 26<br>Tx : 12<br>@ 3.75 V           | 20   | DK                 | 925 – 960 MHz                            |

| UAA2073AM         | LNA + IRM +<br>Tx down-convert mixer            | 3.6 – 5.3              | Rx : 26<br>Tx : 12<br>@ 3.75 V           | 20   | DK                 | 925 – 960 MHz                            |

| Integrated Fro    | nt-End Systems                                  |                        |                                          |      |                    |                                          |

| SA611             | LNA + Mixer                                     | 2.7 – 5.5              | 7 mA<br>@ 3 V                            | 20   | DK                 | LNA 1.2 GHz                              |

|                   |                                                 |                        | @ 3 V                                    |      |                    | Mixer 1.2 GHz                            |

| SA621             | LNA + Mixer + VCO                               | 2.7 – 5.5              | 12/9.3 <sup>(1)</sup> @ 3 V              | 20   | DK                 | LNA 1.2 GHz                              |

|                   |                                                 |                        |                                          |      |                    | Mixer 1.2 GHz                            |

| Mixer Systems     | <u> </u>                                        |                        |                                          |      | <b>L</b>           | · .                                      |

| SA602A            | Mixer + Oscillator                              | 4.5 – 8.0              | 2.4 @ 6 V                                | 8    | N, D               | 500 MHz                                  |

| SA612A            | Mixer + Oscillator                              | 4.5 – 8.0              | 2.4 @ 6 V                                | 8    | N, D               | 500 MHz                                  |

#### Selection guide

| POWER<br>GAIN<br>(dB) | NOISE<br>FIGURE<br>(dB) | INPUT IP3<br>(dBm)    | 1 dB<br>COMP.<br>(dBm) | IMAGE<br>REJECTION<br>(dB) | INPUT<br>IMPED.       | OUTPUT<br>IMPED. | FEATURE<br>HIGHLIGHTS                                         |

|-----------------------|-------------------------|-----------------------|------------------------|----------------------------|-----------------------|------------------|---------------------------------------------------------------|

| F <sub>RF</sub> = 2 G |                         |                       |                        |                            |                       |                  |                                                               |

| 22                    | 4.5                     | LB : 9<br>HB : 12     | 24 – 25                | 35                         | 50 Ω                  | 50 Ω             | Dual-band 800 MHz &<br>1.9 GHz Tripple-mode<br>AMPS/DAMPS/PCS |

| 22                    | 4.5                     | LB : 9<br>HB : 12     | 24 – 25                | 35                         | 50 Ω                  | 50 Ω             | Dual-band<br>900 MHz & 1.5 GHz                                |

| 30                    | 5.8                     | -25                   | -33                    | 34                         | 190 Ω<br>0.8 pF diff. | 50 Ω<br>asym.    | RF to IF DECT transceiver (DSH)                               |

| 20                    | 4.3                     | -17                   | -22                    | 32                         | 60 Ω<br>1 pF diff.    | 1 kΩ diff.       | 3.15 V, 4.3 dB DECT<br>front-end (DSH)                        |

| 20                    | 4.3: DCS                | <b>–17</b>            | -23                    | 32                         | 60 Ω<br>1 pF diff.    | 1 kΩ diff.       | DCS 1800 front-end                                            |

| 22                    | 3.8: DCS<br>4.0: PCS    | -17                   | -24                    | 38                         | 60 Ω<br>0.8 pF diff.  | 1 kΩ diff.       | PCS1900/DCS1800<br>front-end                                  |

| F <sub>RF</sub> = 900 | GHz                     |                       |                        | 1                          |                       | <u> </u>         |                                                               |

| 23                    | 3.25                    | <b>–15</b>            | -23                    | 37                         | 150 Ω<br>1 pF diff.   | 1 kΩ diff.       | 3.6 V phase 2 GSM receiver                                    |

| 22                    | 3.6                     | -15                   | -23                    | 45                         | 150 Ω<br>1 pF diff.   | 1 kΩ diff.       | GSM high IF                                                   |

| F <sub>RF</sub> = 900 | GHz                     |                       | <u> </u>               | <u> </u>                   |                       |                  |                                                               |

| 15/–20 <sup>(1)</sup> | 1.9                     | -5/+25 <sup>(1)</sup> | -16                    |                            | 50 Ω                  | 50 Ω             | Low voltage     Exellent Noise Figure                         |

| Mixer<br>1.2 GHz      | 7                       | 9.5                   | +4                     | -9                         |                       | 50 Ω             | LNA Overload Mode                                             |

| 15/–20 <sup>(1)</sup> | 1.9                     | -5/+25 <sup>(1)</sup> | -16                    |                            | 50 Ω                  | 50 Ω             | Low Voltage     Excellent Noise Figure     LNA Overload Mode  |

| 7                     | 9.5                     | +4                    | -9                     |                            | 50 Ω                  | High             | Low Phase-Noise     Internal VCO                              |

| Mixer F <sub>RF</sub> | = 45 MHz                |                       |                        |                            |                       |                  |                                                               |

| 17                    | 5.0                     | -13                   | -25                    |                            | 1.5 kΩ                | 1.5 kΩ           | Excellent Noise Figure     High Gain                          |

| 17                    | 5.0                     | -13                   | -25                    |                            | 1.5 kΩ                | 1.5 kΩ           | Excellent Noise Figure     High Gain                          |

1997 Dec 15

#### Selection guide

|           | DESCRIPTION <sup>(3)</sup> | V <sub>CC</sub><br>(V) | I <sub>CC</sub><br>(mA)                           | PINS | Pkg <sup>(2)</sup> | INPUT<br>FREQUENCY |

|-----------|----------------------------|------------------------|---------------------------------------------------|------|--------------------|--------------------|

| RF Amplif | iers                       |                        |                                                   |      |                    | - 12 1             |

| SA5200    | Dual Gain Stage            | 4.0 – 9.0              | 4.2/95 μA <sup>(1)</sup> @ 5 V<br>(per) (amplif.) | 8    | D                  | DC - 1.2 GHz       |

| SA5204A   | Wideband Amp               | 5.0 – 8.0              | 25 @ 6 V                                          | 8    | N, D               | DC – 350 MHz       |

| SA5205A   | Wideband Amp               | 5.0 – 8.0              | 25 @ 6 V                                          | 8    | N, D               | DC – 550 MHz       |

| SA5209    | Variable Gain Amp          | 4.5 – 7.0              | 43 @ 5 V                                          | 16   | N, D               | DC – 850 MHz       |

| SA5219    | Variable Gain Amp          | 4.5 – 7.0              | 43 @ 5 V                                          | 16   | N, D               | DC – 700 MHz       |

#### Notes

- 1. Amplifier: Enabled/Disabled

- 2. Package Descriptions:

- a) D: = Small Outline (SO14/16/20)

- b) N: = Dual In-line (DIL)

- c) DK: = Shrink Small Outline Package (SSOP20)

- d) BE: = Low Quad Flat Package (LQFP)

- IRM: Image Reject Mixer

LNA: Low Noise Amplifier

DSH: Double Superheterodyne

diff.: differential asym.: asymmetrical

#### Selection guide

| POWER<br>GAIN<br>(dB)                         | NOISE<br>FIGURE<br>(dB)  | INPUT IP3<br>(dBm) | 1 dB<br>COMP.<br>(dBm) | IMAGE<br>REJECTION<br>(dB) | INPUT<br>IMPED. | OUTPUT<br>IMPED. | FEATURE<br>HIGHLIGHTS                            |

|-----------------------------------------------|--------------------------|--------------------|------------------------|----------------------------|-----------------|------------------|--------------------------------------------------|

| RF F <sub>RF</sub> = 90                       | 0 MHz (NE/S              | A 5200), 100       | MHz (others            | 3)                         |                 |                  |                                                  |

| 7.5/13.5 <sup>(1)</sup><br>(per)<br>(amplif.) | 3.6                      | -1.8               | +3.2                   |                            | 50 Ω            | 50 Ω             | DC to 1.2 GHz     Operation     Power- Down Mode |

| 19                                            | 6.0 (50 Ω)<br>4.8 (75 Ω) | -2                 | +4                     |                            | 50 Ω            | 50 Ω             | DC to 350 MHz     Operation                      |

| 19                                            | 6.0 (50 Ω)<br>4.8 (75 Ω) | -2                 | +4                     |                            | 50 Ω            | 50 Ω             | DC to 550 MHz     Operation                      |

| 25<br>(voltage)                               | 9.3                      | +13<br>(output)    | -3                     |                            | 1.2 Ω           | 60 Ω             | DC to 850 MHz     Operaton                       |

|                                               |                          |                    |                        | , the same                 |                 |                  | Gain Control Pin                                 |

| 25<br>(voltage)                               | 9.3                      | +13<br>(output)    | <del>-</del> 3         |                            | 1.2 Ω           | 60 Ω             | DC to 700 MHz     Operation                      |

|                                               |                          |                    |                        |                            |                 |                  | Gain Control Pin                                 |

#### Notes

- 1. Amplifier: Enabled/Disabled

- 2. Package Descriptions:

- a) D: = Small Outline (SO14/16/20)

- b) N: = Dual In-line (DIL)

- c) DK: = Shrink Small Outline Package (SSOP20)

- d) BE: = Low Quad Flat Package (LQFP)

- IRM: Image Reject Mixer LNA: Low Noise Amplifier DSH: Double Superheterodyne

diff.: differential asym.: asymmetrical

#### Front-end, Discrete

#### Selection guide

FRONT-END, DISCRETE

|                                       | SYSTEM     |            |             |                         | GAIN                 | NOISE                | GAIN                 | NOISE                |        |         | PACKAGE               |        |        |

|---------------------------------------|------------|------------|-------------|-------------------------|----------------------|----------------------|----------------------|----------------------|--------|---------|-----------------------|--------|--------|

| SOCKET                                | FREQ.      | Ic<br>(MA) | <b>S</b> (S | F <sub>T</sub><br>(GHz) | (dB)<br>@ 900<br>MHz | (dB)<br>@ 900<br>MHz | (dB)<br>@ 1.9<br>GHz | (dB)<br>@ 1.9<br>GHz | SOT23  | SOT323  | SOT343 <sup>(1)</sup> | SOT353 | SOT363 |

| LNA                                   | 006        | 3          | 4.5         | 17                      | 20                   | ٦                    | 22                   | 1.6                  |        |         | BFG403W               |        |        |

|                                       | 900 & 1900 | 2-5        | 3-12        | 6                       | 17                   | 1.2                  | 10                   | 1.9                  | BFR505 | BFS505  | BFG505W               | BFC505 | BFM505 |

|                                       | 900 & 1900 | 3-30       | 3-12        | 6                       | 17                   | 1.2                  | 10                   | 1.9                  | BFR520 | BFS520  | BFG520W               | BFC520 | BFM520 |

|                                       | 900 & 1900 | 1-10       | 2 – 4.5     | 22                      | 21                   | 1.2                  | 53                   | 6.0                  | -      |         | BFG410W               |        | , ,    |

| · · · · · · · · · · · · · · · · · · · | 900 & 1900 | 3-25       | 2 – 4.5     | 22                      | 20                   | 1.2                  | 28                   | 0.8                  |        |         | BFG425W               |        |        |

| Mixer                                 | 006        | 5-30       | 3 – 10      | 9                       | 13                   | 1.9                  |                      |                      | BFR93A | BFR93AW | BFG93AW               |        |        |

|                                       | 900 & 1900 | 2-5        | 3 – 12      | 6                       | 17                   | 1.2                  | 10                   | 1.9                  | BFR505 | BFS505  | BFG505W               | BFE505 | BFM505 |

|                                       | 900 & 1900 | 3-30       | 3-12        | 6                       | 17                   | 1.2                  | 10                   | 1.9                  | BFR520 | BFS520  | BFG520W               | BFE520 | BFM520 |

|                                       | 900 & 1900 | 1 - 10     | 2-4.5       | 22                      | 21                   | 1.2                  | 59                   | 6.0                  |        |         | BFG410W               |        | ls.    |

|                                       | 900 & 1900 | 3-25       | 2-4.5       | 22                      | 20                   | 1.2                  | 28                   | 9.0                  |        |         | BFG425W               |        |        |

| Buffer &                              | 006        | 3-20       | 3 – 10      | 9                       | 14                   | 2.1                  |                      |                      | BFR92A | BFR92AW |                       |        |        |

| 3                                     | 006        | 5-30       | 3 – 10      | 9                       | 13                   | 1.9                  |                      |                      | BFR93A | BFR93AW |                       |        |        |

|                                       | 900 & 1900 | 2-5        | 3 – 12      | 6                       | 17                   | 1.2                  | 10                   | 1.9                  | BFR505 | BFS505  | BFG505W               | BFC505 | BFM505 |

|                                       | 900 & 1900 | 3-30       | 3 – 12      | 8                       | 17                   | 1.2                  | 10                   | 1.9                  | BFR520 | BFS520  | BFG520W               | BFC520 | BFM520 |

|                                       | 900 & 1900 | 1-10       | 2-4.5       | 22                      | 21                   | 1.2                  | 59                   | 6.0                  |        |         | BFG410W               |        |        |

| e e Visione                           | 900 & 1900 | 3-25       | 2 – 4.5     | 22                      | 20                   | 1.2                  | 28                   | 8.0                  |        | -       | BFG425W               |        |        |

| 些                                     | 40 – 100   | 3-20       | 3-12        | 1.2                     | 20                   | 20 dB gain @ 100 MHz | 100 MH.              | 2                    | BF547  | BF547W  |                       | -      |        |

|                                       | 100 – 250  | 3-20       | 3 - 8       | 2.8                     | 25                   | 25 dB gain @         | 250 MHz              | 2                    | BFS17A | BFS17W  |                       |        |        |

|                                       | >250       | 3-20       | 3 – 10      | 2                       | 25                   | 25 dB gain @         | 500 MHz              | 2                    | BFR92A | BFR92AW |                       |        |        |

|                                       |            |            |             |                         |                      |                      |                      |                      |        |         |                       |        |        |

22

1. Typically the gain is 2 - 3 dB higher in SOT343 packages.

#### **IF systems**

#### Selection guide

#### IF SYSTEMS

|             |                        |                              |      |                  | INPUT          | IF            | FRF                                           | = 45 MHz              |                                     |

|-------------|------------------------|------------------------------|------|------------------|----------------|---------------|-----------------------------------------------|-----------------------|-------------------------------------|

|             | V <sub>CC</sub><br>(V) | Icc                          | PINS | Pkg              | FREQ.<br>(MHz) | FREQ<br>(MHz) | INPUT<br>SENSI-<br>TIVITY                     | MIXER<br>GAIN<br>(dB) | INPUT<br>IP <sub>3</sub><br>(dBm)   |

| FM IF       |                        |                              |      |                  |                |               |                                               |                       |                                     |

| SA604A      | 4.5 – 8                | 3.3 mA @ 6 V                 | 16   | D,N              | 25             | 25            | 0.22(1)                                       |                       | - ·                                 |

| SA614A      | 4.5 – 8                | 3.3 mA @ 6 V                 | 16   | D,N              | 25             | 25            | 0.22(1)                                       |                       | -                                   |

| SA624       | 4.5 – 8                | 3.4 mA @ 6 V                 | 16   | D,N              | 25             | 25            | 0.22(1)                                       | - · ·                 |                                     |

| Mixer/FM II | =                      |                              |      |                  |                |               | * *: * · · · · · · · · · · · · · · · · ·      |                       |                                     |

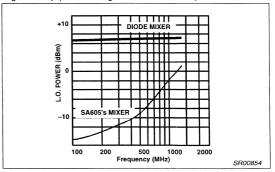

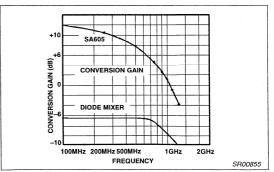

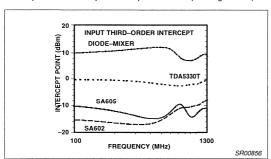

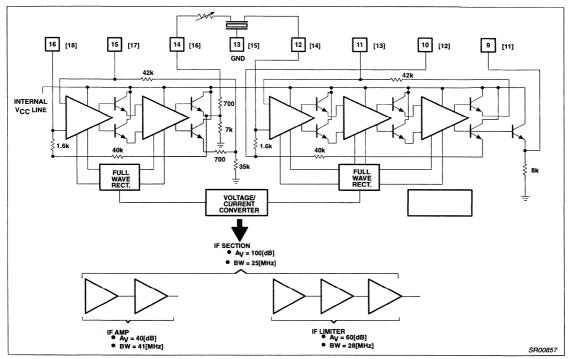

| SA605       | 4.5 – 8                | 5.7 mA @ 6 V                 | 20   | D,DK,N           | 500            | 25            | 0.22                                          | 13                    | -10                                 |

| SA615       | 4.5 – 8                | 5.7 mA @ 6 V                 | 20   | D,DK,N           | 500            | 25            | 0.22                                          | 13                    | -10                                 |

| SA625       | 4.5 – 8                | 5.8 mA @ 6 V                 | 20   | D,DK,N           | 500            | 25            | 0.22                                          | 13                    | -10                                 |

| Low Voltag  | e Mixer/FN             | 1 IF                         |      | All San Comments |                |               |                                               |                       |                                     |

| SA606       | 2.7 – 7                | 3.5 mA @ 3 V                 | 20   | D,DK,N           | 150            | 2             | 0.31                                          | 17                    | -9                                  |

| SA616       | 2.7 – 7                | 3.5 mA @ 3 V                 | 20   | D,DK,N           | 150            | 2             | 0.31                                          | 17                    | -9                                  |

| SA676       | 2.7 – 5.5              | 3.5 mA @ 3 V                 | 20   | D,DK             | 100            | 2             | 0.45                                          | 17                    | -10                                 |

| SA607       | 2.7 – 7                | 3.5 mA @ 3 V                 | 20   | D,DK,N           | 150            | 2             | 0.31                                          | 17                    | -9                                  |

| SA608       | 2.7 – 7                | 3.5 mA @ 3 V                 | 20   | D,DK,N           | 150            | 2             | 0.31                                          | 17                    | -9                                  |

| SA626       | 2.7 – 5.5              | 6.5 mA @ 3 V                 | 20   | D,DK             | 500            | 25            | 0.54 <sup>(2)</sup>                           | 11(2)                 | -16 <sup>(2)</sup>                  |

| SA636       | 2.7 – 5.5              | 6.5mA @ 3V                   | 20   | D,DK             | 500            | 25            | 0.54(2)                                       | 11(2)                 | -16 <sup>(2)</sup>                  |

| SA639       | 2.7 – 5.5              | 8.5 mA @ 3 V                 | 24   | DH               | 500            | 25            | 2.24(4)                                       | 12(4)                 | -12.5 <sup>(4)</sup>                |

| Low Voltag  | ge Mixer/Di            | gital IF                     |      |                  | <del></del>    |               |                                               |                       | <del>Vigoronia, se de la como</del> |

| SA637       | 2.7 – 5.5              | 3.5 mA @ 3 V                 | 20   | D,DK             | 200            | 2             | $\frac{-117 \text{ dBm}^3}{0.31 \mu\text{V}}$ | 7                     | -17                                 |

| SA647       | 2.7 – 5.5              | 5.9 @ 3 V                    | 20   | DK               | 200            | 2             | -112 dBm                                      |                       | -28                                 |

| SA1630      | 2.7 – 5.5              | Tx: 26.5<br>Rx: 33.5<br>@3 V | 48   | BE               | 400            |               |                                               |                       |                                     |

| SA1638      | 2.7 – 5.5              | Tx: 22<br>Rx: 18<br>@3 V     | 48   | BE               | 400            | . 1           |                                               |                       |                                     |

#### IF systems

#### Selection guide

| RSSI<br>RANGE<br>(dB) | FAST<br>RSSI | FREQ.<br>CHECK PIN | IF<br>FILTER<br>MATCH<br>(kHz) | OUTPUT<br>OP AMPS                                               | FEATURE HIGHLIGHTS                                                                       |

|-----------------------|--------------|--------------------|--------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------|

| FM IF                 |              |                    |                                |                                                                 |                                                                                          |

| 90                    |              |                    | 455                            | - · ·                                                           | High Sensitivity                                                                         |

| 80                    | -            | -                  | 455                            | -                                                               | Wide IF BW                                                                               |

| 90                    | Х            | -                  | 455                            | -                                                               |                                                                                          |

| Mixer/FM              | IF           | <u> </u>           |                                |                                                                 |                                                                                          |

| 90                    | -            | <del>-</del>       | 455                            | -                                                               | High Sensitivity                                                                         |

| 80                    | -            | -                  | 455                            | -                                                               | High Input Frequency                                                                     |

| 90                    | х            | -                  | 455                            | -                                                               |                                                                                          |

| Low Volta             | ge Mixe      | r/FM IF            | -                              |                                                                 |                                                                                          |

| 90                    | -            | -                  | 455                            | Audio Op Amp<br>RSSI Op Amp                                     | High Sensitivity                                                                         |

| 80                    | -            | -                  | 455                            | Audio Op Amp<br>RSSI Op Amp                                     | Low Power                                                                                |

| 70                    | -            | -                  | 455                            | Audio Op Amp<br>RSSI Op Amp                                     | Audio Op Amp     RSSI Buffered                                                           |

| 90                    | -            | ×                  | 455                            | Audio Op Amp<br>RSSI Op Amp                                     | Audio/RSSI     Output Op Amps                                                            |

| 90                    | -            | х                  | 455                            | Audio Buffered<br>RSSI Op Amp                                   | • Power-Down Mode (SA626/636/639)                                                        |

| 90                    | х            | -                  | 10.7 MHz                       | Audio Buffered<br>RSSI Op Amp                                   |                                                                                          |

| 90                    | х            | -                  | 10.7 MHz                       | RSSI Op Amp                                                     |                                                                                          |

| 90                    | х            | -                  | 10.7 MHz                       | Audio Buffered<br>RSSI Op Amp<br>Post-detect Amp<br>Data Switch |                                                                                          |

| Low Volta             | age Mixe     | r/Digital IF       |                                |                                                                 |                                                                                          |

| 90                    | х            | -                  | 455 kHz                        | RSSI Op Amp                                                     |                                                                                          |

| 90                    | ×            | -                  | 455 kHz                        | RSSI Op Amp                                                     | Improved mixer gain and sensetivity over SA637                                           |

|                       |              |                    |                                |                                                                 | Wireless LAN using DSSS modulation     Digital IF Gain Control of 70 dB in steps of 2 dB |

|                       |              |                    |                                |                                                                 | GSM 900 Mhz     DCS 1.8 GHz     uadrature up & down mixer stage                          |

#### IF systems

#### Selection guide

#### Notes

- 1. Measured with a Philips MESA602A mixer prior to the IF input.

- 2. Measured at f<sub>RF</sub> = 240 MHz.

- 3. Represents the -3 dB Input Limiting point (dBm). Also shown in  $\mu$ V units into a 50  $\Omega$  matching network.

- 4. Measured at f<sub>RF</sub> = 110 MHz.

#### **Temperature Ranges**

SA: -40 to +85 °C.

#### Package DescriptionsIF Filter Match

D:

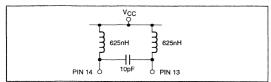

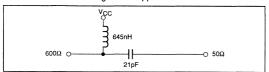

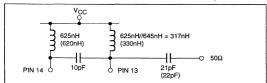

Small Outline - 16 DK: Shrink Small Outline Package (SSOP) - 20455 kHz = 1.5 k $\Omega$  Small Outline - 20 N: Dual In-Line Plastic - 16, 2010.7 MHz = 330  $\Omega$ .

#### **IF Filter Match**

$455~\text{kHz} = 1.5~\text{k}\Omega$

10.7 MHz = 330  $\Omega$ .

#### Frequency synthesizers

#### Selection guide

#### **FREQUENCY SYNTHESIZERS**

|               | V <sub>cc</sub> | Icc             | PINS   | Pkt         | MAX<br>RF/INPUT<br>FREQ.              | CHANNEL<br>SPACING | FRACTIONAL<br>-N<br>DIVIDER | AUXILIARY<br>SYNTHE-<br>SIZER | APPLICA-<br>TIONS                                                        |

|---------------|-----------------|-----------------|--------|-------------|---------------------------------------|--------------------|-----------------------------|-------------------------------|--------------------------------------------------------------------------|

| Fractional    | -N Frequ        | ency Syr        | thesiz | ers         |                                       |                    |                             |                               |                                                                          |

| SA<br>7016DH  | 2.7 to<br>5.5 V | 5 mA<br>@ 3 V   | 16     | TSSOP<br>16 | 1.3 GHz                               |                    | х                           |                               | IS-54/-136,<br>IS-95,<br>PDC,<br>GSM<br>digital<br>cellular              |

| SA<br>7025DK  | 2.7 to<br>5.5 V | 7.5 mA<br>@ 3 V | 20     | SSOP<br>20  | 1.0 GHz<br>(main)<br>150 MHz<br>(aux) |                    | x                           | x                             | IS-54/-136,<br>IS-95,<br>PDC,<br>GSM<br>digital<br>cellular              |

| SA<br>7026DK  | 2.7 to<br>5.5 V | 6.5 mA<br>@ 3 V | 20     | SSOP<br>20  | 1.3 GHz<br>(main)<br>550 MHz<br>(aux) |                    | х                           | х                             | IS-54/-136,<br>IS-95,<br>PDC,<br>GSM<br>digital<br>cellular              |

| SA<br>8016DH  | 2.7 to<br>5.5 V | 6.5 mA<br>@ 3 V | 16     | TSSOP<br>16 | 2.5 GHz                               |                    | х                           |                               | ISM band,<br>IS-54/-136,<br>IS-95,<br>PDC,<br>GSM<br>digital<br>cellular |

| SA<br>8025ADK | 2.7 to<br>5.5 V | 11 mA<br>@ 3 V  | 20     | SSOP<br>20  | 1.8 GHz<br>(main)<br>150 MHz<br>(aux) |                    | х                           | x                             | PHS digital cordless, U.S. PCS, PDC digital cellular                     |

| SA<br>8026DK  | 2.7 to<br>5.5 V | 8.5 mA<br>@ 3 V | 20     | SSOP<br>20  | 2.5 GHz<br>(main)<br>550 MHz<br>(aux) |                    | х                           | х                             | ISM band,<br>IS-54/-136,<br>IS-95,<br>PDC,<br>GSM<br>digital<br>cellular |

#### Frequency synthesizers

#### Selection guide

|               | V <sub>cc</sub> | Icc              | PINS | Pkt        | MAX<br>RF/INPUT<br>FREQ.               | CHANNEL<br>SPACING | FRACTIONAL<br>-N<br>DIVIDER | AUXILIARY<br>SYNTHE-<br>SIZER | APPLICA-<br>TIONS                                                       |

|---------------|-----------------|------------------|------|------------|----------------------------------------|--------------------|-----------------------------|-------------------------------|-------------------------------------------------------------------------|

| Frequenc      | y Synthe        | sizers           |      |            |                                        |                    |                             |                               |                                                                         |

| UMA<br>1015M  | 2.6 to<br>5.5 V | 9 mA<br>@ 3 V    | 20   | SSOP<br>20 | 1.1 GHz<br>1.1 GHz                     | 5 – 1000<br>kHz    |                             | x<br>(dual)                   | AMPS/TA<br>CS cellular<br>CT1/CT2<br>cordless                           |

| UMA<br>1015AM | 2.7 to<br>5.5 V | 8.7 mA<br>@ 3 V  | 20   | SSOP<br>20 | 1.1 GHz                                | 5 – 1000<br>kHz    |                             | x<br>(dual)                   | AMPS/TA<br>CS cellular<br>lower cost<br>replaceme<br>nt of UMA<br>1015M |

| UMA<br>1018M  | 2.7 to<br>5.5 V | 10 mA<br>@ 5.5 V | 20   | SSOP<br>20 | 1250 MHz<br>(main)<br>300 MHz<br>(aux) | 10 – 2000<br>kHz   |                             | X                             | GSM<br>digital<br>cellular                                              |

| UMA<br>1020M  | 2.7 to<br>5.5 V | 12 mA<br>@ 5.5 V | 20   | SSOP<br>20 | 2400 MHz<br>(main)<br>300 MHz<br>(aux) | 10 – 2000<br>kHz   |                             | x                             | DECT<br>digital<br>cordless,<br>DCS 1800,<br>PHS                        |

| UMA<br>1021M  | 2.7 to<br>5.5 V | 10 mA<br>@ 5.5 V | 20   | SSOP<br>20 | 2200 MHz                               | 10 – 2000<br>kHz   |                             |                               | GSM,<br>WLAN,<br>DECT<br>digital<br>cordless,<br>DCS 1800,<br>PHS       |

| UMA<br>1022M  | 2.7 to<br>5.5 V | 13 mA<br>@ 3 V   | 20   | SSOP<br>20 | 2200 MHz<br>(main)<br>500 MHz<br>(aux) | 10 – 2000<br>kHz   |                             | х                             | 900 MHz<br>& 2 GHz<br>applic-<br>ations                                 |

#### Frequency synthesizers

#### Selection guide

|              | V <sub>cc</sub> | Icc             | PINS | Pkt         | MAX<br>INPUT<br>FREQ. | MAX<br>COM-<br>PARE<br>FREQ. | INPUT<br>SENSITIVITY | DIVIDE RATIO   |

|--------------|-----------------|-----------------|------|-------------|-----------------------|------------------------------|----------------------|----------------|

| Prescaler    | s               |                 |      |             |                       |                              |                      |                |

| SA<br>701N,D | 2.7 to<br>6 V   | 4.5 mA<br>@ 3 V | 8    | DIP,<br>S08 | 1.1 GHz               | 65 kHz/<br>270 kHz           | –35 dBm              | 128/129, 64/65 |

| SA<br>702N,D | 2.7 to<br>6 V   | 4.5 mA<br>@ 3 V | 8    | DIP,<br>S08 | 1.1 GHz               | 1000 kHz                     | –35 dBm              | 64/66/72       |

#### Transmitters ICs

#### Selection guide

| TYPE     | FREQUENCY<br>RANGE<br>(OUTPUT)<br>(MHz) | FREQUENCY<br>RANGE<br>(SYNTHESIZER)<br>(MHz) | SUPPLY<br>VOLTAGE<br>(V) | lcc<br>(FULL<br>POWER)<br>(mA) | DIFFERENTIAL<br>OUTPUT<br>(dBm) | TRANSMIT<br>OFFSET<br>FREQUENCY<br>(MHz) | PACKAGE | FEATURE<br>HIGHLIGHTS |

|----------|-----------------------------------------|----------------------------------------------|--------------------------|--------------------------------|---------------------------------|------------------------------------------|---------|-----------------------|

| CELLULAR | ~                                       |                                              |                          | -                              |                                 |                                          |         |                       |

| SA900    | 820 - 860 (AMPS)                        | N/A                                          | 4.5 – 5.1                | 42 (AMPS)                      | 2                               | 90 – 140                                 | LQFP48  | BICMOS I/Q            |

|          | 820 - 920 (Dual)                        |                                              |                          | 68 (Dual)                      |                                 |                                          |         | transmit RF           |

|          |                                         |                                              |                          |                                |                                 |                                          |         | modulator             |

|          |                                         |                                              |                          |                                |                                 |                                          |         | with on-chip crys-    |

|          |                                         |                                              |                          |                                |                                 |                                          |         | tal osc. and VCO      |

| SA9025   | 820 - 920 (Dual)                        | 800 – 2.200                                  | 3.6 – 3.9                | 95 (AMPS)                      | +                               | 90 – 180                                 | LQFP48  | Higly integrated      |

|          | 1.840 - 1.920 (PCS)                     |                                              |                          | 52(Dual)                       |                                 |                                          |         | I/Q transmit          |

|          | with ext. up-conv.                      |                                              |                          |                                |                                 |                                          |         | RF- modulator         |

|          | •                                       |                                              |                          |                                |                                 |                                          |         | with 2.2 GHz dual     |

|          |                                         |                                              |                          |                                |                                 |                                          |         | synth. for 800 &      |

|          |                                         |                                              | -                        |                                |                                 |                                          |         | 1900 Tripple          |

|          |                                         |                                              |                          |                                |                                 |                                          |         | mode TDMA             |

TRANSMITTERS ICS

FEATURE HIGHLIGHTS

PACKAGE

#### **MMICs Amplifiers**

2 W DCS/PCS Power

Amplifier

GaAs MMIC

LQFP48

GaAs MMIC 4 W GSM Power Amplifier

LQFP48

#### Selection guide

|                  | EFFICIENC<br>(%)         |          | 55                                          | 45            | 35            |

|------------------|--------------------------|----------|---------------------------------------------|---------------|---------------|

|                  | POWER GAIN<br>(dB) MIN.  |          | 34                                          | 35.5          | 32            |

|                  | OUTPUT<br>POWER<br>(dBm) |          | 34                                          | 35.5          | 24            |

|                  | LOAD POWER<br>(W)        |          | 3.2                                         | 4             | 0.5           |

|                  | SUPPLY<br>VOLTAGE<br>(V) |          | 4.8                                         | 3.6           | 2.7 – 5.5     |

| FIERS            | FREQUENCY<br>BAND        |          | CGY2021G 1.71 – 1.785 or<br>1.85 – 1.91 GHz | 880 – 915 MHz | 820 - 905 MHz |

| MMICS AMPLIFIERS | TYPE                     | CELLULAR | CGY2021G                                    | CGY2013G      | SA910         |

| 199              | 7 Dec 15                 |          |                                             |               |               |

| _                |                 |           |     |      |    |    |        |                                                               |

|------------------|-----------------|-----------|-----|------|----|----|--------|---------------------------------------------------------------|

| SA910            | 820 - 905 MHz   | 2.7 – 5.5 | 0.5 | 24   | 32 | 35 | SSOP20 | SSOP20 BICMOS Low-voltage 900 MHz variable gain pre-amplifier |

| CORDLESS         |                 |           |     |      |    |    |        | -                                                             |

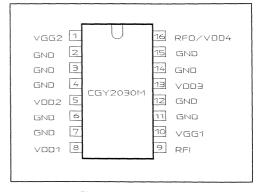

| CGY2030M 1.88 -  | 1.88 – 1.90 GHz | 3.6       | 0.5 | 27   | 27 | 40 | SSOP16 | SSOP16 GaAs MMIC 500 mW amplifier                             |

| CGY2032TS 1.88 - | 1.88 – 1.90 GHz | 3.6       | 0.5 | 27   | 27 | 50 | SSOP16 | SSOP16 GaAs MMIC 500 mW amplifier                             |

| WLAN (ISM band)  | and)            |           |     |      |    |    |        |                                                               |

| SA2410           | 2.4 – 2.5 GHz   | 3.0 – 5.5 |     | 18.5 | 59 | 25 | TQFP32 | TQFP32 2.5 GHz power amplifier and T/R switch for             |

WLAN (ISM-band)

# MODULE AMPLIFIERS

Note

1. Objective specification

#### Discrete Amplifiers

#### Selection guide

# DISCRETE AMPLIFIERS

| TYPE               | FREQUENCY<br>(MHz)        | SUPPLY<br>VOLTAGE | LOAD POWER<br>(W) | POWER GAIN<br>(dB) | EFFICIENCY<br>(%) | ENCY<br>6) | THERMAL<br>RESISTANCE <sup>3</sup><br>(K/W) | PACKAGE       |

|--------------------|---------------------------|-------------------|-------------------|--------------------|-------------------|------------|---------------------------------------------|---------------|

|                    |                           | Ē                 |                   | Ż                  | N<br>N<br>N       | TYP.       |                                             |               |

| ANALOG CELLULAR    | ULAR                      |                   |                   |                    |                   |            |                                             |               |

| BLT80              | 006                       | 7.5               | 0.8               | 9                  | 09                | 29         | 224                                         | SOT223        |

| BLT81              | 006                       | 7.5               | 1.2               | 9                  | 09                | 20         | 325                                         | SOT223        |

| BLT80              | 006                       | 0.9               | 0.8               | 7 (typ.)           |                   | 22         | 224                                         | SOT223        |

| BLT81              | 006                       | 6.0               | 1.2               | 6.5 (typ.)         |                   | 20         | 325                                         | SOT223        |

| BLT70              | 006                       | 4.8               | 9.0               | 9                  | 09                |            | 39 <sup>6</sup>                             | SOT223        |

| BLT71              | 006                       | 4.8               | 1.2               | 9                  | 09                |            | 247                                         | SOT223        |

| BLT71/8            | 006                       | 4.8               | 1.2               | 11                 | 55                | 63         | 20                                          | SOT96         |

| BLT61 <sup>2</sup> | 006                       | 3.6               | 1.2               | 10                 | 20                | 63         | 358                                         | SOT96 (SO8pl) |

| DIGITAL CELLU      | DIGITAL CELLULAR/CORDLESS |                   |                   |                    |                   |            |                                             |               |

| BFG540W            | 006                       | 9                 | 18 dBm            | 18                 |                   |            |                                             | SOT343        |

| BFG540W            | 1900                      | 3.6               | 14 dBm            | 11                 |                   |            |                                             | SOT343        |

| BFG10W/x           | 006                       | 9                 | 28 dBm            | 10                 |                   |            |                                             | SOT343        |

| BFG10W/x           | 1900                      | 3.6               | 20 dBm            | 9                  |                   |            |                                             | SOT343        |

| BFG11W/x           | 1900                      | 3.6               | 26 dBm            | 9                  |                   |            |                                             | SOT343        |

| BFG21W             | 1900                      | 3.6               | 0.4               | 11                 | 20                |            |                                             | SOT343        |

| BLT82              | 006                       | 0.9               | 3.5               | 8                  | 50                | 65         | 329                                         | SOT96 (SO8pl) |

#### Discrete Amplifiers

#### Selection guide

| APPLICATION | SUPPLY VOLTAGE<br>(V) | LOAD POWER<br>(W) | 1st STAGE | 2nd STAGE | 3rd STAGE |

|-------------|-----------------------|-------------------|-----------|-----------|-----------|

| Analog      | 6.0                   | 1.2               | BFG540W/x | BLT80     | BLT81*    |

|             | 4.8                   | 1.2               | BFG540W/x | BLT70     | BLT71     |

|             | 3.6                   | 1.2               | BFG520W/x | BFG10W/x  | BLT61     |

| -           | 4.8                   | 1.2               | BFG10W/x  | BLT71/8   |           |

| GSM         | 6.0                   | 3.5               | BFG520W/x | BFG10W/x  | BLT82     |

| DECT, PHS   | 3.6                   | 0.4               | BFG540/x  | BFG10/x   | BFG11/x   |

|             |                       |                   | BFG540W/x | BFG10W/x  | BFG11W/x  |

|             |                       |                   | BFG425W   | BFG21W    |           |

Notes

1. Objective specification

Preliminary specification

Junction to soldering joint

Surface of the second of the se

6. P<sub>tot</sub> = 2 W, T<sub>g</sub> = 95 °C 7. P<sub>tot</sub> = 3.5 W, T<sub>g</sub> = 90 °C 8. P<sub>tot</sub> = 2 W, T<sub>g</sub> = 115 °C

9.  $P_{tot} = 1.9 \text{ W, } T_g = 115 \,^{\circ}\text{C}$

33

#### Baseband processors

#### Selection guide

**BASEBAND PROCESSORS**

|                 | PART TYPE                           | APPLICATION  | V <sub>DD</sub> | loo                                 | PACKAGE                        |

|-----------------|-------------------------------------|--------------|-----------------|-------------------------------------|--------------------------------|

| PCD5041         | BMC (Burst Mode Controller)         | DECT         | 2.7 – 6.0       | 15 mA Typ. Active                   | 64-Pin QFP                     |

| PCD5042         | BMC (Burst Mode Controller)         | DECT         | 2.7 – 6.0       | 15 mA Typ. Active                   | 64-Pin QFP                     |

| PCD5043         | BMC (Burst Mode Controller)         | DECT         | 2.7 – 6.0       | 15 mA Typ. Active                   | 64-Pin QFP                     |

| PCD5091/2/3/4/5 | Baseband Processor                  | DECT         | 2.7 – 3.6       | 1                                   | QFP 100<br>LOFP 100            |

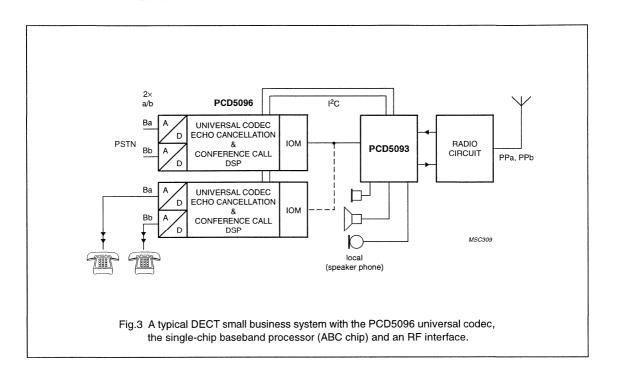

| PCD5096         | Universal Codec                     | DECT<br>ISDN | 2.7 – 3.6       | -                                   | QFP 44                         |

| PCF5083         | Signal Processor                    | GSM/DCS/PCS  | 2.7 – 3.6       |                                     | 128-Pin LQFP                   |

| PCF507X         | Baseband & Audio Interface          | GSM/DCS/PCS  | 2.7 - 3.6       |                                     | 80-Pin LQFP                    |

| P90CL301        | 16-bit Low Voltage Micro Controller | GSM/DCS/PCS  | 2.7 – 3.6       | -                                   |                                |

| PCF5077         | Power Amplifier Controllers         | GSM/DCS/PCS  | 2.7 – 5.5       |                                     | SSOP16                         |

| SA5752          | Audio Companding VOX and Amplifier  | AMPS<br>TACS | 2.7 – 5.5       | 3.1 mA Тур.<br>125 µA Stdby         | 20-Pin SOL<br>20-Pin SSOP      |

| SA5753          | Audio Filter and Control            | AMPS<br>TACS | 3.0 – 5.5       | 1.7 mA Typ.<br>600 μA Stdby         | 20-Pin SOL<br>20-Pin SSOP      |

| UMA1002         | Data processor for cellular radio   | AMPS<br>TACS | 2.7 – 5.5       | 0.8 mA Typ.                         | 28-Pin SOL<br>32-Pin LQFP      |

| PCF5001         | POCSAG decoder                      | PAGERS       | 1.5 – 6.0       | 60 µА Тур.                          | 28-Pin Mini-Pack<br>32-Pin QFP |

| PCD5002         | APOC1/POCSAG decoder                | PAGERS       | 1.5             | 50 µA Typ.                          | 32-Pin LQFP                    |

| PCD5003         | Advanced POCSAG paging decoder      | PAGERS       | 1.5 – 6.0       | 50 μΑ Typ. (ON)<br>25 μΑ Typ. (OFF) | 32-Pin LQFP                    |

| PCD5008         | FLEX decoder                        | PAGERS       | 1.8 – 3.3       | 6.8 μA Typ.                         | 32-Pin LQFP                    |

## Compandors

## Selection guide

|       | Vcc      | ၁၁၂                       | PINS | PINS PACKAGES | ALC               | REFERENCE<br>VOLTAGE | UNITY               | POWER<br>DOWN  | KEY FEATURES                                              | APPLICATIONS                                                |

|-------|----------|---------------------------|------|---------------|-------------------|----------------------|---------------------|----------------|-----------------------------------------------------------|-------------------------------------------------------------|

| SA570 | 6 – 24 V | 3.2 mA                    | 16   | D, F, N       | Both<br>channels  | Fixed 1.8 V          | 775 mVms            | o <sub>N</sub> | -Excellent unity gain<br>tracking error<br>-Excellent THD | High<br>Performance<br>Audio Circuits                       |

|       |          |                           |      |               |                   |                      |                     | -              |                                                           | "Hi-Fi Commer-<br>cial Quality"                             |

| SA571 | 6 – 18 V | 3.2 mA                    | 16   | D, F, N       | Both              | Fixed 1.8 V          | 775 mVms            | o<br>N         | -Excellent unity gain tracking error                      | High Perform-<br>ance Audio                                 |

|       |          |                           |      |               | cramers           |                      |                     |                | -Excellent                                                | Circuits<br>"Hi-Fi Commer-<br>cial Quality"                 |

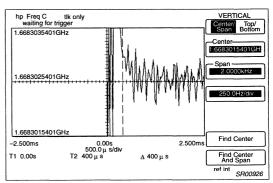

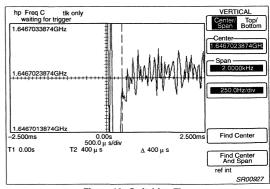

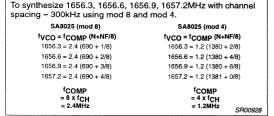

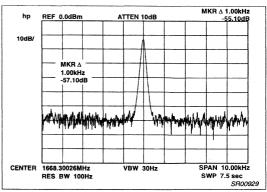

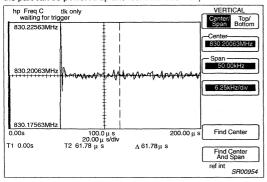

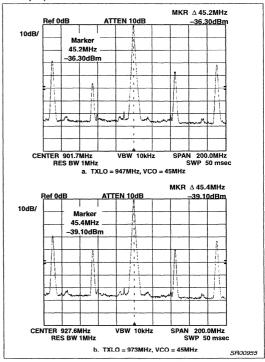

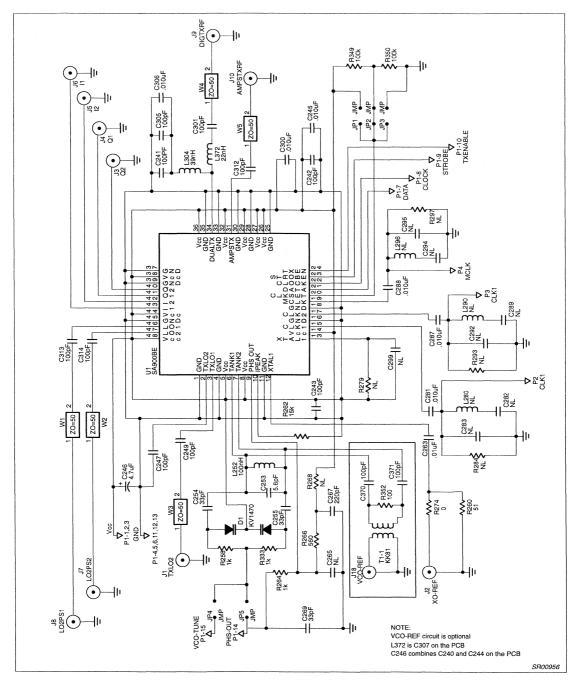

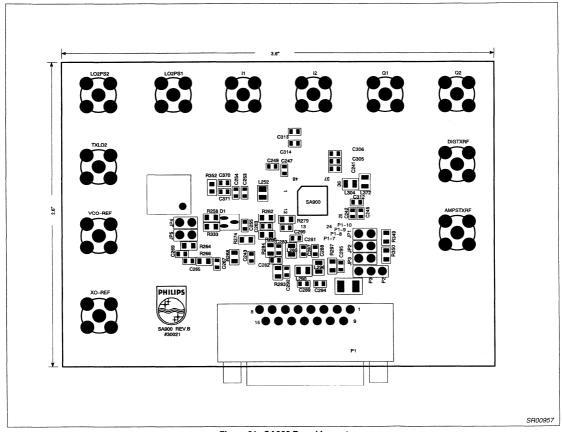

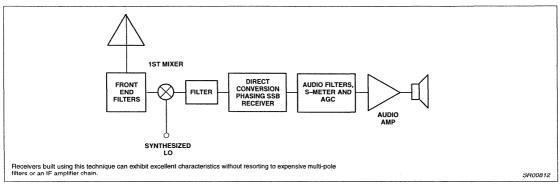

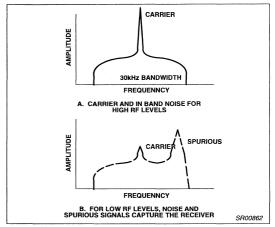

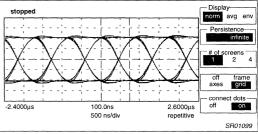

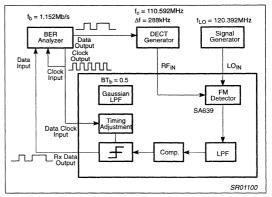

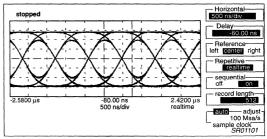

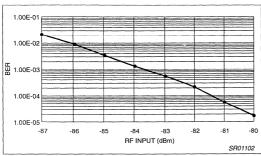

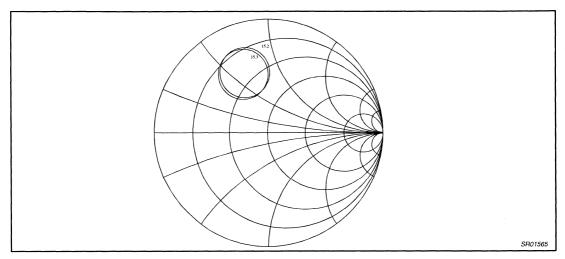

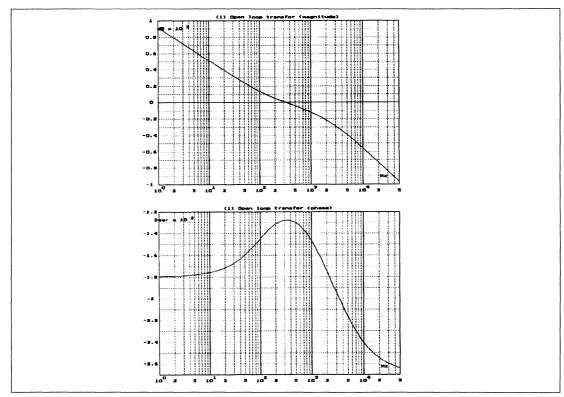

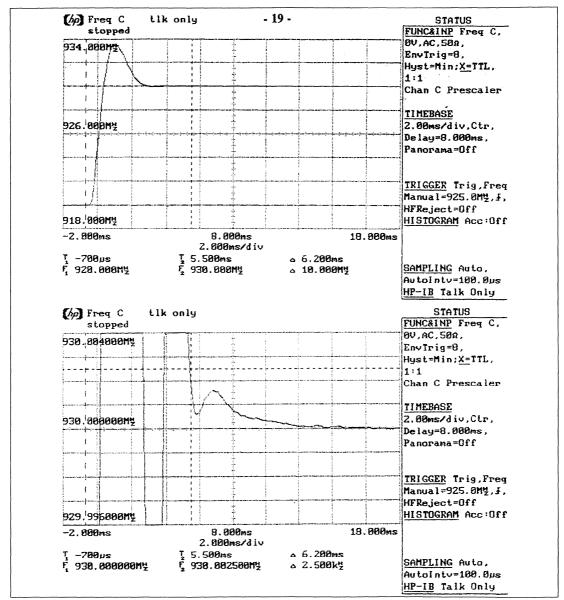

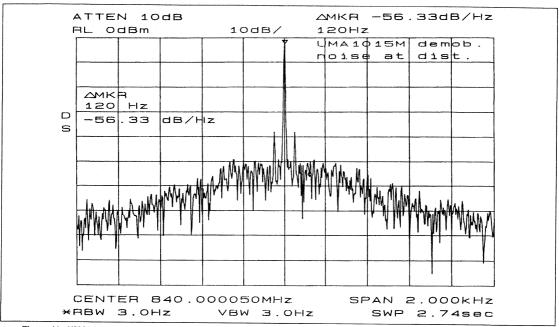

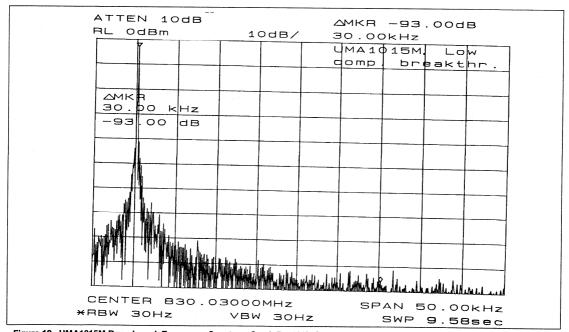

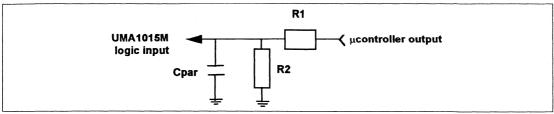

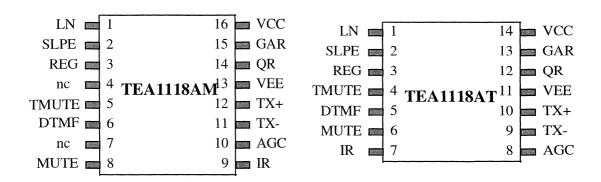

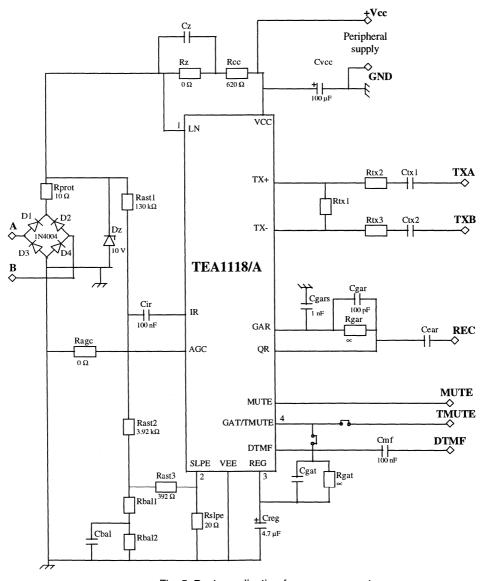

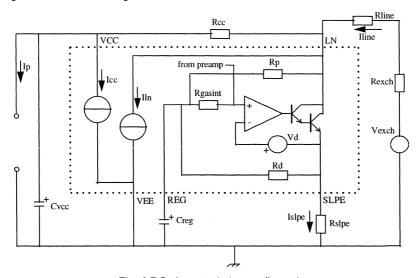

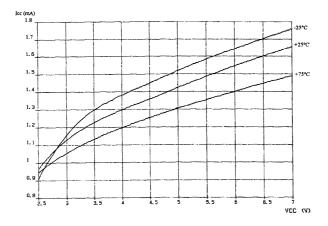

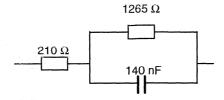

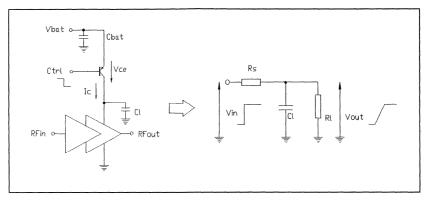

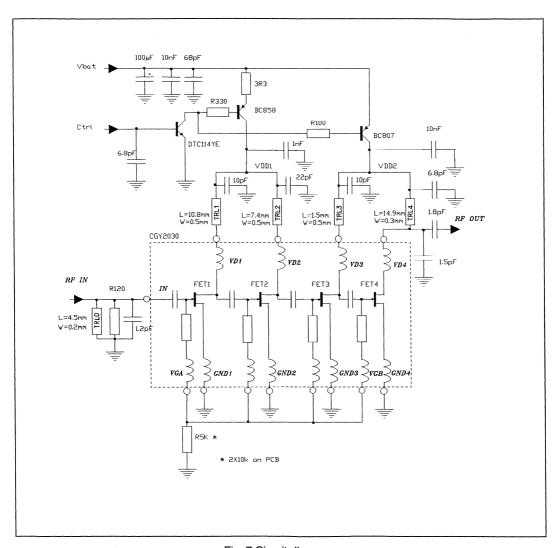

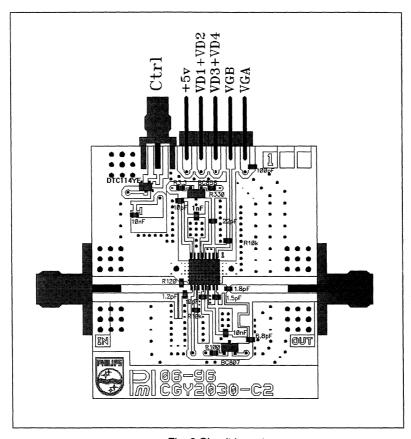

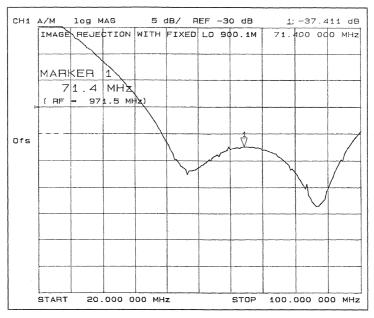

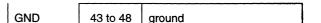

| SA572 | 6 – 22 V | 6 mA                      | 16   | D, F, N       | Both              | Fixed 2.5 V          | 100 MVms            | o<br>N         | -Independent attack & release time                        | High Perform-<br>ance Audio                                 |